# ES FIS FIC AN AVNEX COMPANY **ESD** Protection ICs Quick reference guide

# Ensuring device safety

ST's large portfolio of protection devices and ICs supports all industry requirements for Electrical overstress (EOS), surge, and electrostatic discharge (ESD) in a complete portfolio.

ST's protection devices have passed all certifications, meeting or exceeding international protection standards for electrical hazards on electronics boards found in the demanding automotive, computer, consumer, industrial and telecom markets.

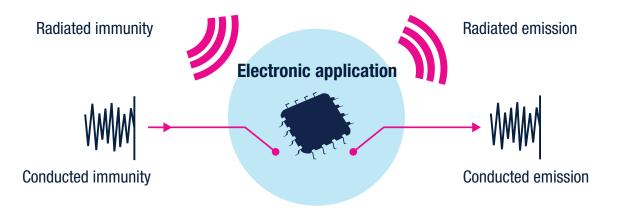

# WHAT IS EMC IMMUNITY?

EMC Immunity is the ability of an equipment to properly operate in its electromagnetic environment by limiting the interference of electromagnetic energy that may cause physical damage.

## **ELECTRO-STATIC DISCHARGE (ESD)**

Electro-Static Discharge (ESD) is defined by the ESD Association as 'the rapid, spontaneous transfer of electrostatic charge induced by a high electrostatic field'. ESD surge waveforms are specified in IEC 61000-4-2. An ESD can be caused by various objects such as production line machines but is mostly generated by human contact. Three major failure mechanisms have been identified:

**Silicon Melting**

**Melting Flesh**

With their increased sensitivity, the implementation of miniature components has raised the risk of ESD. It is essential to protect industrial, automotive and IoT applications having connectors exposed to human contact. Furthermore, the Industry Council Worldwide Survey shows that 30% of IC field returns are due to ESD.

It therefore seems necessary to protect ICs with external ESD protections.

# HOW TO CHOOSE THE RIGHT ESD PROTECTION IC FOR AN APPLICATION ?

We have put together a list of criteria to help you select the appropriate ESD protection IC for your device.

Transparency

During normal operation (no surge event), the ESD protection IC must have the least possible impact on the system's performance (such as power consumption or frequency bandwidth).

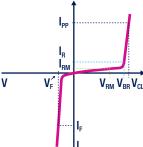

- V<sub>RM</sub>: standoff voltage. It defines the normal operating voltage for the protection. V<sub>RM</sub> must be higher than the application's maximum operating voltage, otherwise the protection will clamp the application voltage.

- Directionality: if the signal to be protected is negative and positive, protection must be bi-directional to avoid the rectifier phenomenon. If the signal to be protected is only positive, then a unidirectional protection should be preferred to avoid a negative ESD clamping voltage. However, a bidirectional protection can also be implemented.

- C<sub>I/O-GND</sub>: line capacitance to ground. The ESD protection diode behaves like a capacitance when high frequencies are reached. This capacitance defines a cut-off frequency that can impact the application's signal integrity. The ESD protection line's capacitance is a key parameter for high-speed interfaces (digital or RF lines).

- Efficiency

- V<sub>CL</sub>: Clamping voltage. This is the maximum voltage across the ESD Protection. When an ESD surge occurs, the ESD protection must lower this surge voltage as close as possible to the V<sub>RM</sub> in order to protect the IC placed behind the ESD protection.

## WHAT ARE THE MAIN BENEFITS OF ST'S SOLUTIONS?

ST's solutions offer quality and reliability. IEC 61000-4-2 Level 4 specifies up to  $\pm 8$  kV contact discharge. ESD protection decreases this  $\pm 8$  kV ESD transient surge down to a residual transient voltage that is harmless for the application. Reduced ppm rate in field return and cost-efficient maintenance ensure products are safely designed for customers.

Easily select components by using ST-PROTECTION-FINDER mobile app available for Android<sup>TM</sup> and iOS<sup>TM</sup> to enter the protection key criteria values ( $V_{RM}$  and  $C_{I/O-GND}$ ) and choose the most appropriate package.

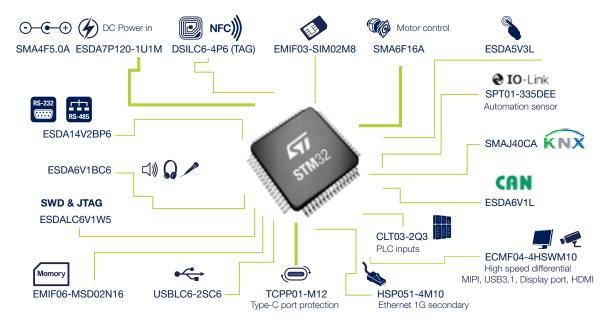

# **RECOMMENDED ESD IC PROTECTION FOR MCU INTERFACES:**

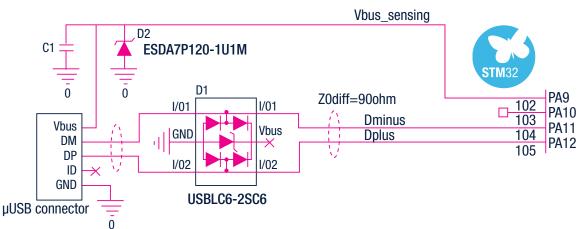

## Example of application USB 2.0 Full speed without OTG:

Design tip: Use a Transient Voltage Suppressor (TVS) to protect against 8/20  $\mu s$  surges on DC power rails.

#### Featured products:

#### USBLC6-2SC6 + ESDA7P120-1U1M

- Compliant with USB2.0 eye diagram

- ESD robustness: 15 kV contact discharge IEC61000-4-2

#### Power rail ESD and EOS protection Low-Speed interface

**Protection IC**

ESDA25P35-1U1M ESDA17P100-1U2M

ESDA17P50-1U1M

ESDA13P70-1U1M SDA7P120-1U1M

|   | Application        | Protection IC |

|---|--------------------|---------------|

|   | RS-232/RS-485      | ESDA14V2BP6   |

|   | Touch button       | ESDA5V3L      |

|   | Audio (ADC)        | ESDA6V1BC6    |

|   | Automation sensor  | SPT01-335DEE  |

|   | Industrial CAN bus | ESDA6V1L      |

| - | SWD & JTAG         | ESDALC6V1W5   |

#### **High-Speed interface**

| Application                                                        | Protection IC  |

|--------------------------------------------------------------------|----------------|

| NFC tag                                                            | DSILC6-4P6     |

| USB                                                                | USBLC6-2SC6    |

| Ethernet 1G (secondary)                                            | HSP051-4M10    |

| High-speed differential<br>(MIPI, USB3.1, Display Port<br>and HDM) | ECMF04-4HSWM10 |

#### **GLOSSARY**

Stand-off voltage (V<sub>PM</sub>)

20 V

15 V

9 V

5 V

AEC-Q101 - Automotive Electronics Council specification related to the qualification of discrete components for Automotive market.

Breakdown voltage (V<sub>BR</sub>) - the voltage value above which the current in the ESD Protection device increases very fast for a slight increase in voltage. This value is usually defined at 1 mA DC.

**EOS** - Electrical Over-Stress

HBM - Human Body Model shows ESD surge in controlled environments like manufacturing lines. Most ICs integrate an HBM protection in their I/O structure. IEC61000-4-2 applies to an application whereas HBM applies to an IC. The level of energy is much higher for system level ESD protection (IEC 61000-4-2).

I<sub>no</sub> - Peak pulse current, corresponds to the maximum current that can flow through a protection IC for a given surge waveform.

I<sub>BM</sub> - Maximum leakage current defined at V<sub>BM</sub>.

Line Capacitance - Equivalent line to ground capacitance for the ESD diode. A lower line capacitance allows a larger bandwidth and a better signal integrity.

TLP method - Transmission Line Pulse. This is a method for measuring the clamping voltage

$V_{cL}$  - clamping voltage value for a current pulse with a peak value of  $I_{PP}$ . Usually,  $V_{cL}$  presented on datasheet is measured with IEC 61000-4-2 8 kV ESD discharge. The clamping voltage obtained at 30ns corresponds to a 16 A TLP response.

$V_{BM}$  - maximum working voltage with associated maximum leakage current ( $I_{BM}$ )