# Avnet UltraZed™-EG SOM Designer's Guide

Version 1.1

# **Document Control**

**Document Version:** 1.1

**Document Date:** 1/25/2017

# **Prior Version History**

| Version | Date      | Comment |

|---------|-----------|---------|

| 1.1     | 1/25/2017 |         |

# **Contents**

| I | Intr | Introduction5                                  |     |  |  |  |  |

|---|------|------------------------------------------------|-----|--|--|--|--|

| 2 | Ultr | aZed-EG SOM                                    | . 6 |  |  |  |  |

| 3 | Ultr | aZed-EG SOM On-board Resources                 | . 8 |  |  |  |  |

|   | 3.1  | Zynq UltraScale+ MPSoC XCZU3EG-1SFVA625 Device | 8   |  |  |  |  |

|   | 3.1. | 1 PS MIO Bank 500                              | 8   |  |  |  |  |

|   | 3.1. | 2 PS MIO Bank 501                              | 8   |  |  |  |  |

|   | 3.1. | 3 PS MIO Bank 502                              | 9   |  |  |  |  |

|   | 3.1. |                                                |     |  |  |  |  |

|   | 3.1. |                                                |     |  |  |  |  |

|   | 3.1. |                                                |     |  |  |  |  |

|   | 3.1. |                                                |     |  |  |  |  |

|   | 3.1. |                                                |     |  |  |  |  |

|   | 3.2  | DDR4 SDRAM                                     |     |  |  |  |  |

|   | 3.3  | Dual Parallel QSPI Flash                       |     |  |  |  |  |

|   | 3.4  | eMMC Flash                                     |     |  |  |  |  |

|   | 3.5  | USB 2.0 PHY                                    |     |  |  |  |  |

|   | 3.6  | Ethernet PHY                                   | 12  |  |  |  |  |

|   | 3.7  | PS Reference Clock Input                       | 12  |  |  |  |  |

|   | 3.8  | MPSoC Real-Time Clock (RTC)                    | 12  |  |  |  |  |

|   | 3.9  | I2C EEPROM                                     | 12  |  |  |  |  |

|   | 3.10 | I2C 8-Bit I/O Expander                         | 13  |  |  |  |  |

|   | 3.11 | 2-Channel I2C Switch/Mux                       | 13  |  |  |  |  |

|   | 3.12 | PS Boot Mode Switch                            | 14  |  |  |  |  |

|   | 3.13 | PMBus Interface                                | 15  |  |  |  |  |

|   | 3.14 | SOM Reset Structure                            | 16  |  |  |  |  |

|   | 3.15 | PS Power-On Reset (POR) Circuit                | 17  |  |  |  |  |

|   | 3.16 | SOM Reset Input                                | 17  |  |  |  |  |

|   | 3.17 | ·                                              |     |  |  |  |  |

|   | 3.18 | MPSoC Heat Sink with Fan                       | 18  |  |  |  |  |

|   | 3.19 | Voltage Regulators                             | 18  |  |  |  |  |

| Oiti | aZed-EG SOM External Interfaces                                                                                                                                      | . 13                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 4.1  | PS MIO Interface                                                                                                                                                     | 21                   |

| 4.2  | PS USB 2.0 Connector Interface                                                                                                                                       | 22                   |

| 4.3  | PS RJ45 Connector Interface                                                                                                                                          | 23                   |

| 4.4  | PS GTR Transceiver Interface                                                                                                                                         | 23                   |

| 4.5  | PL HD I/O Pins                                                                                                                                                       | 24                   |

| 4.6  | PL HP I/O Pins                                                                                                                                                       | 24                   |

| 4.7  | PL SYSMON Interface                                                                                                                                                  | 24                   |

| 4.8  | SOM Reset Input                                                                                                                                                      | 25                   |

| 4.9  | Carrier Card Reset Output                                                                                                                                            | 25                   |

| 4.10 | Carrier Card I2C Interface                                                                                                                                           | 26                   |

| 4.11 | Ethernet MAC ID                                                                                                                                                      | 26                   |

| 4.12 | JTAG Interface                                                                                                                                                       | 27                   |

| 4.13 | PMBus Interface                                                                                                                                                      | 28                   |

| 4.14 | Power Requirements                                                                                                                                                   | 29                   |

| 4.15 | Power Sequencing                                                                                                                                                     | 30                   |

| 4.16 | Power Estimation Using XPE                                                                                                                                           | 30                   |

| 4.17 | MPSoC Heat Sink with Fan                                                                                                                                             | 30                   |

| Ultr | aZed-EG SOM JX Micro Connectors                                                                                                                                      | . 31                 |

| 5.1  | Custom Carrier Cards Mating JX Receptacle Connectors                                                                                                                 | 31                   |

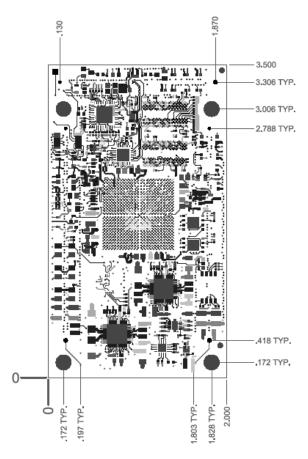

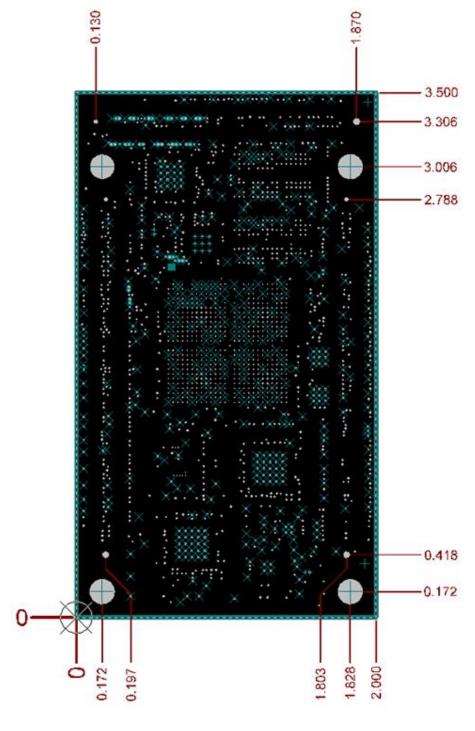

| Ultr | aZed-EG SOM Mechanical Dimensions                                                                                                                                    | . 39                 |

| Car  | rier Card PCB Design Guidelines                                                                                                                                      | 40                   |

| 7.1  | Connector Land and Alignment                                                                                                                                         |                      |

| 7.2  | USB and Ethernet Connector Signal Routing                                                                                                                            | .40                  |

| 7.3  | PS GTR Transceiver Signal Routing                                                                                                                                    |                      |

| 7.4  | PS MIO Routing                                                                                                                                                       | .41                  |

| 7.5  | PL SYSMON Signal Routing                                                                                                                                             | .41                  |

| 7.6  | PL Single-Ended and Differential Signal Routing                                                                                                                      | .42                  |

| 7.7  | JTAG Interface Signal Routing                                                                                                                                        | .42                  |

| 7.8  | VIN Decoupling Caps                                                                                                                                                  | .42                  |

| 7.9  | Mechanical Considerations                                                                                                                                            | .43                  |

| 7.10 | Thermal Considerations                                                                                                                                               | 44                   |

| Get  | tting Help and Support                                                                                                                                               | 46                   |

|      |                                                                                                                                                                      |                      |

|      |                                                                                                                                                                      |                      |

|      |                                                                                                                                                                      | 53                   |

|      | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.10<br>4.11<br>4.15<br>4.16<br>4.17<br>Ultr<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.7<br>7.8<br>7.10<br>Get<br>JX1 | 4.1 PS MIO Interface |

# 1 Introduction

This document provides guidelines for designing custom Carrier Cards for the Avnet UltraZed-EG SOM. It includes reference schematics for implementing various UltraZed-EG™ SOM external interfaces as well as the Carrier Card PCB design guidelines.

| Term   | Definition                                       |

|--------|--------------------------------------------------|

| PS     | Zynq UltraScale+ MPSoC Processing System         |

| PL     | Zynq UltraScale+ MPSoC <i>Programmable Logic</i> |

| MIO    | PS Multiplexed Input Output Pins                 |

| POR    | Power On Reset                                   |

| APU    | Application Processing Unit                      |

| RPU    | Real-time Processing Unit                        |

| GPU    | Graphics Processing Unit                         |

| SYSMON | System Monitor                                   |

| HD     | High Density PL I/O Pins                         |

| HP     | High Performance PL I/O Pins                     |

| PMBus  | Power Management Bus                             |

Glossary

#### **Additional Documentation**

Additional information and documentation on Xilinx's Zynq<sup>®</sup> UltraScale+™ MPSoC can be found at <a href="http://www.xilinx.com/products/silicon-devices/soc/zynq-ultrascale-mpsoc.html">http://www.xilinx.com/products/silicon-devices/soc/zynq-ultrascale-mpsoc.html</a>. Additional information and documentation on UltraZed-EG can be found at <a href="http://www.ultrazed.org/product/ultrazed-EG">www.ultrazed.org/product/ultrazed-EG</a>.

## 2 UltraZed-EG SOM

Avnet UltraZed-EG SOM is a highly integrated System-on-Module (SOM) designed based on the Xilinx powerful Zynq UltraScale+ MPSoC family of devices. Designed in a small form factor, the UltraZed-EG SOM packages all the necessary functions such as system memory, Ethernet, USB, and configuration memory needed for an embedded processing system. Although, initially released with the Xilinx XCZU3EG device, the UltraZed-EG SOM will be pin and form factor compatible with the XCZU2EG or XCZU3CG/XCZU2CG (UltraZed-CG) versions using the MPSoC device in the same package as the XCZU3EG device.

The UltraZed-EG SOM is offered in commercial and industrial temperatures and supports the following features:

- Xilinx XCZU3EG-1SFVA625 device

- DDR4 SDRAM (2GB, x32)

- Dual QSPI Flash (64MB)

- I2C EEPROM (2Kb)

- eMMC Flash (8GB, x8)

- USB 2.0 ULPI PHY

- Gigabit Ethernet PHY

- I2C 8-bit I/O expander

- 2-channel I2C switch/mux

- PS reference clock input

- On-board PMBus voltage regulators

- Power-On Reset (POR) circuit

- A 4-position boot mode DIP switch

- 3 JX micro-header connectors (2 x 140-pin, 1 x 100-pin) providing the following connections to the custom Carrier Cards (signal directions are with respect to the UltraZed-EG SOM):

- 180 user PL I/O pins

- 26 user PS MIO pins (one full MIO bank)

- 4 PS GTR transceivers

- 4 PS GTR reference clock inputs

- PS JTAG interface

- PL SYSMON interface

- USB 2.0 connector interface

- Gigabit Ethernet RJ45 connector interface

- PMBus interface

- SOM PS VBATT battery input

- Carrier Card I2C interface

- SOM Reset input

- Carrier Card interrupt input

- Carrier Card Reset output

- Power Good output

- SOM to Carrier Card ground pins

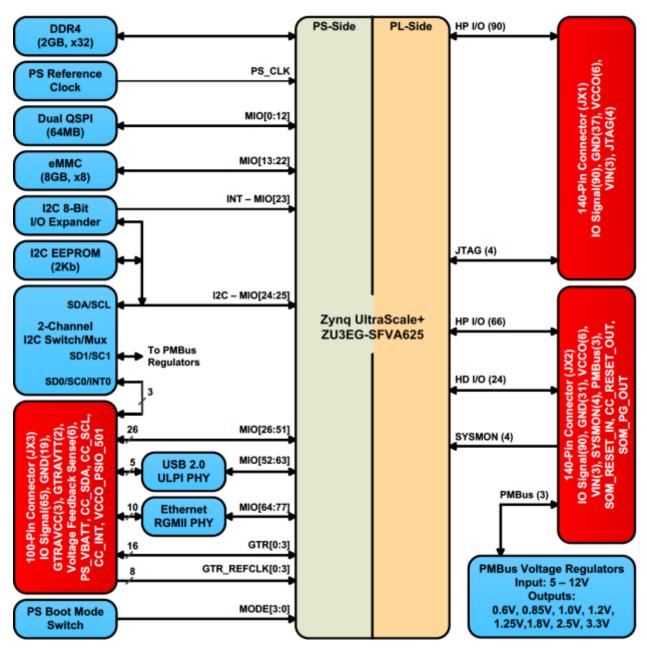

- SOM input voltages and output sense pins

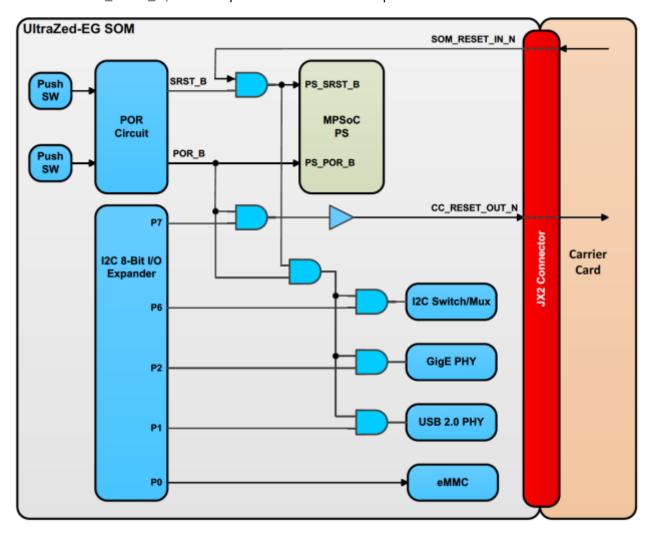

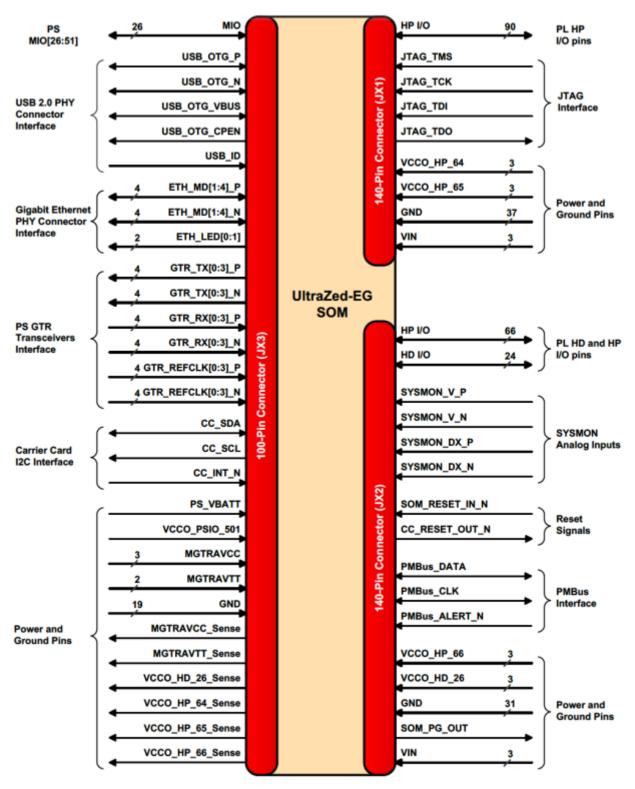

The UltraZed-EG SOM high-level block diagram is shown in the following figure. The interfaces to the Zynq UltraScale+ MPSoC device on the UltraZed-EG SOM are divided into Processing System (PS) side and Programmable Logic (PL) side. The following sections describe the UltraZed-EG SOM on-board resources and external interfaces to the Carrier Cards.

Figure 1 – UltraZed-EG SOM Block Diagram

## 3 UltraZed-EG SOM On-board Resources

The following sections provide a brief description of each component/resource available on the UltraZed-EG SOM.

Please refer to the Avnet UltraZed-EG SOM schematic at the end of this document for more information on the UltraZed-EG SOM on-board resources.

## 3.1 Zyng UltraScale+ MPSoC XCZU3EG-1SFVA625 Device

The UltraZed-EG SOM utilizes the Xilinx **XCZU3EG-SFVA625** device in -1 speed grade part (the UltraZed-EG SOM is designed to support all speed grades for the XCZU3EG-SFVA625 device). The XCZU3EG-1SFVA625 device supports APU speed of 1.2GHz (max), RPU speed of 500MHz (max), GPU speed of 600MHz (max), and DDR4 speed of up to 2133Mbps. The ZU3EG-A625 device features the following resources:

- 78 PS MIO pins (3 banks of MIOs, PS banks 500, 501, and 502, with 26 pins/bank)

- 4 PS GTR transceivers along with 4 PS GTR reference clock inputs (PS bank 505)

- PS DDR4 x32 interface (PS bank 504)

- PS JTAG interface (PS bank 503)

- Real-Time Clock (PS bank 503)

- PL SYSMON interface (PL bank 0)

- 24 PL HD (High Density) I/O pins (PL bank 26)

- 156 PL HP (High Performance) I/O pins (PL banks 64, 65, and 66)

The following sections provide brief descriptions of how each XCZU3EG MPSoC bank is used on the Avnet UltraZed-EG SOM followed by detail descriptions in subsequent sections.

#### 3.1.1 PS MIO Bank 500

The PS MIO bank 500 consists of 26 MIO pins, MIO[0:25]. The MIO pins for this bank are operated at 1.8V and used to implement the following interfaces on the UltraZed-EG SOM:

- Dual Parallel (x8) QSPI Flash

- eMMC x8 Flash

- I2C EEPROM (2Kb)

- I2C 8-bit I/O expander

- I2C 2-channel switch/mux

- Carrier Card I2C interface

- I2C interface to the PMBus voltage regulators

#### 3.1.2 PS MIO Bank 501

The PS bank 501 consists of 26 MIO pins, MIO[26:51]. These MIO pins are routed to the JX3 connector and are available to the custom Carrier Cards. The PS bank 501 I/O can be operated at 1.8V, 2.5V, or 3.3V set by the user via JX3 connector. This full bank of MIO pins can be used on a custom Carrier Card to implement various interfaces. On the Avnet UltraZed IO Carrier Card, PS MIO bank 501 are operated at 3.3V and used to implement the following interfaces:

- microSD card

- Dual USB-UART ports

- PS PMOD header

- PS user LED and push switch

- Display Port auxiliary interface

#### 3.1.3 PS MIO Bank 502

The PS bank 502 consists of 26 MIO pins, MIO[52:77]. The MIO pins for this bank are operated at 1.8V and used to implement the following interfaces on the UltraZed-EG SOM (please refer to the USB 2.0 PHY and Ethernet PHY sections of this document for more information):

- USB 2.0 ULPI PHY interface

- Gigabit Ethernet RGMII PHY interface

#### 3.1.4 PS Bank 503

The PS bank 503 consists of JTAG, reset, PS reference clock input, boot mode, RTC crystal input, and few configuration pins. The reset, PS reference clock input, boot mode, RTC crystal input, and the configuration pins of the PS bank 503 pins are used on the UltraZed-EG SOM while the JTAG pins are routed to the JX1 connector. The PS bank 503 I/O is operated at 1.8V.

Zynq UltraScale+ MPSoC provides a built-in Real-Time Clock (RTC). A 32.768 KHz crystal is connected to the PS bank 503 **PS\_PADI** and **PS\_PADO** pins for the RTC. The on-chip RTC uses the **PS\_VBATT** pin (provided by the Carrier Card via JX3 connector) for the backup battery. Carrier Cards drive the **PS\_VBATT** pin with a 1.5V battery.

#### 3.1.5 PS Bank 504

The PS bank 504 consists of DDR4 interface pins. These pins are used on the UltraZed-EG SOM to implement the DDR4 x32 memory interface. The PS bank 504 I/O is operated at 1.2V.

#### 3.1.6 PS Bank 505

The PS bank 505 consists of PS GTR transceiver and their associated reference clock input pins (PS provides 4 GTR transceivers along with 4 reference clock inputs). These pins are routed to the JX3 connector and are available to the custom Carrier Cards. The GTR transceiver power rails (0.85V and 1.8V) are supplied by the custom Carrier Cards via JX3 connector.

#### 3.1.7 PL Bank 0

The PL bank 0 consists of System Monitor (**SYSMON**) pins. These pins are routed to the JX2 connector and are available to the custom Carrier Cards. The System Monitor supply voltages (VCCADC and VREF) are provided on the UltraZed-EG SOM.

#### 3.1.8 PL Bank 26, 64, 65, and 66

The PL HD bank 26 and HP banks 64, 65, and 66 provide 24 HD (High Density, bank 26) and 156 HP (High Performance, banks 64, 65, and 66) I/O pins. These pins are routed to the JX1/JX2 connectors and are available to the custom Carrier Cards. The PL HP banks I/O pins can be operated at 1.0V-1.8V while the PL HD bank I/O pins can be operated at 1.2V-3.3V. The VCCO voltages for the PL HD and HP banks are provided by the custom Carrier Cards via JX1/JX2 connectors.

#### 3.2 DDR4 SDRAM

The UltraZed-EG SOM provides 2GB of DDR4 memory in x32 configuration using 2 Micron MT40A512M16JY-083E IT:B (96-pin BGA package) x16 devices. This device is implemented in 512Mb x 16 configuration and supports up to 2400Mbps data rate. The DDR4 devices are connected to the PS bank 504 and operated at 1.2V.

## 3.3 Dual Parallel QSPI Flash

The UltraZed-EG SOM provides 64MB of QSPI Flash in dual-parallel (x8) configuration. Two Micron MT25QU256ABA1EW7-0SIT (8-pin W-PDFN package) devices are used to implement the parallel Flash interface on the UltraZed-EG SOM. The QSPI Flash devices are connected to the PS MIO bank 500 and operated at 1.8V I/O. The QSPI Flash can be used as a primary boot device on the UltraZed-EG SOM.

| Signal Name  | MIO Pin# | Notes                         |

|--------------|----------|-------------------------------|

| CLK_1        | MIO[0]   | Lower QSPI device clock       |

| DATA[1]_1    | MIO[1]   | Lower QSPI device DATA[1]     |

| DATA[2]_1    | MIO[2]   | Lower QSPI device DATA[2]     |

| DATA[3]_1    | MIO[3]   | Lower QSPI device DATA[3]     |

| DATA[0]_1    | MIO[4]   | Lower QSPI device DATA[0]     |

| CS_1         | MIO[5]   | Lower QSPI device chip select |

| Feedback CLK | MIO[6]   | No Connect                    |

| CS_2         | MIO[7]   | Upper QSPI device chip select |

| DATA[0]_2    | MIO[8]   | Upper QSPI device DATA[0]     |

| DATA[1]_2    | MIO[9]   | Upper QSPI device DATA[1]     |

| DATA[2]_2    | MIO[10]  | Upper QSPI device DATA[2]     |

| DATA[2]_2    | MIO[11]  | Upper QSPI device DATA[3]     |

| CLK_2        | MIO[12]  | Upper QSPI device clock       |

Table 1 - Dual-Parallel QSPI Flash Interface Pin Assignments

#### 3.4 eMMC Flash

The UltraZed-EG SOM provides 8GB of eMMC Flash to be used as a primary and/or secondary boot device. A single Micron MTFC8GAKAJCN-4M IT (153-pin VFBGA package) device is used to implement the eMMC Flash x8 interface. The eMMC device is connected to the PS MIO bank 500 and operated at 1.8V I/O. P0 port of the SOM I2C 8-bit I/O expander can be used to soft reset the eMMC device (please refer to the I2C 8-Bit I/O Expander section of this document for more information).

| Signal Name | MIO Pin# | Notes        |

|-------------|----------|--------------|

| DATA[0]     | MIO[13]  | eMMC DATA[0] |

| DATA[1]     | MIO[14]  | eMMC DATA[1] |

| DATA[2]     | MIO[15]  | eMMC DATA[2] |

| DATA[3]     | MIO[16]  | eMMC DATA[3] |

| DATA[4]     | MIO[17]  | eMMC DATA[4] |

| DATA[5]     | MIO[18]  | eMMC DATA[5] |

| DATA[6]     | MIO[19]  | eMMC DATA[6] |

| DATA[7]     | MIO[20]  | eMMC DATA[7] |

| CMD         | MIO[21]  | eMMC Command |

| CLK         | MIO[22]  | eMMC Clock   |

Table 2 – eMMC Flash Interface Pin Assignments

## 3.5 USB 2.0 PHY

The UltraZed-EG SOM provides a single USB 2.0 PHY interface using the Microchip USB3320 USB 2.0 ULPI PHY in 32-pin QFN package. The USB 2.0 ULPI PHY connector side (connected to the JX3 connector) along with the PS USB 3.0 port (PS GTR[x]), connected to the JX3 connector) can be used on custom Carrier Cards to implement a USB 2.0/3.0 interface via a single connector. Please refer to the <a href="UltraZed-EG SOM External Interfaces">UltraZed-EG SOM External Interfaces</a> section of this document for more information.

The USB 2.0 ULPI PHY host side I/O is connected to the PS MIO bank 502 and operated at 1.8V on the UltraZed-EG SOM. P1 port of the I2C 8-bit I/O expander can be used to soft reset the USB 2.0 ULPI PHY (please refer to the I2C 8-Bit I/O Expander section of this document for more information). Custom Carrier Cards have the option of not implementing the USB 3.0 portion of this interface.

| Signal Name | MIO Pin# | Notes                                      |

|-------------|----------|--------------------------------------------|

| CLK         | MIO[52]  | ULPI PHY clock input                       |

| DIR         | MIO[53]  | Controls the direction of the data bus     |

| DATA[2]     | MIO[54]  | Host side DATA[2]                          |

| NXT         | MIO[55]  | This signal is used to throttle the data   |

| DATA[0]     | MIO[56]  | Host side DATA[0]                          |

| DATA[1]     | MIO[57]  | Host side DATA[1]                          |

| STP         | MIO[58]  | Stops the data stream currently on the bus |

| DATA[3]     | MIO[59]  | Host side DATA[3]                          |

| DATA[4]     | MIO[60]  | Host side DATA[4]                          |

| DATA[5]     | MIO[61]  | Host side DATA[5]                          |

| DATA[6]     | MIO[62]  | Host side DATA[6]                          |

| DATA[7]     | MIO[63]  | Host side DATA[7]                          |

Table 3 – USB 2.0 ULPI PHY Host Interface Side Pin Assignments

#### 3.6 Ethernet PHY

The UltraZed-EG SOM provides a single Gigabit Ethernet PHY interface using the TI **DP83867** RGMII PHY device in 48-pin QFN package. The UltraZed-EG SOM Gigabit Ethernet PHY connector side (connected to the JX3 connector) along with an RJ45 connector located on the custom Carrier Card can be used to implement a Gigabit Ethernet port.

The TI DP83867 RGMII Ethernet PHY host side I/O is connected to the PS MIO bank 502 and operated at 1.8V on the UltraZed-EG SOM. P2 port of the I2C 8-bit I/O expander can be used to soft reset the Gigabit Ethernet PHY while P3 port of this I/O expander can be used to put the Gigabit Ethernet PHY in a Power Down mode (please refer to the I2C 8-Bit I/O Expander section of this document for more information).

| Signal Name | MIO Pin# | Notes                 |

|-------------|----------|-----------------------|

| TX_CLK      | MIO[64]  | Transmit clock        |

| TX_DATA[0]  | MIO[65]  | Transmit DATA[0]      |

| TX_DATA[1]  | MIO[66]  | Transmit DATA[1]      |

| TX_DATA[2]  | MIO[67]  | Transmit DATA[2]      |

| TX_DATA[3]  | MIO[68]  | Transmit DATA[3]      |

| TX_CTL      | MIO[69]  | Transmit control      |

| RX_CLK      | MIO[70]  | Receive clock         |

| RX_DATA[0]  | MIO[71]  | Receive DATA[0]       |

| RX_DATA[1]  | MIO[72]  | Receive DATA[1]       |

| RX_DATA[2]  | MIO[73]  | Receive DATA[2]       |

| RX_DATA[3]  | MIO[74]  | Receive DATA[3]       |

| RX_CTL      | MIO[75]  | Receive control       |

| MDC         | MIO[76]  | Management Data Clock |

| MDIO        | MIO[77]  | Management Data I/O   |

Table 4 – RGMII PHY Interface Host Interface Side Pin Assignments

## 3.7 PS Reference Clock Input

The UltraZed-EG SOM provides a 33.33 MHz single-ended 1.8V reference clock input to the Zynq UltraScale+ MPSoC PS block.

## 3.8 MPSoC Real-Time Clock (RTC)

Zynq UltraScale+ MPSoC provides a built-in Real-Time Clock (RTC). A 32.768KHz crystal is connected to the PS bank 503 **PS\_PADI** and **PS\_PADO** pins for the RTC. The on-chip RTC uses the **PS\_VBATT** pin (provided by the custom Carrier Card via JX3 connector) for the backup battery. Custom Carrier Cards drive the **PS\_VBATT** pin with a 1.5V battery.

## 3.9 I2C EEPROM

The UltraZed-EG SOM provides 2Kb of I2C EEPROM using the Atmel **AT34C02D-MAHM-T** (8-pin UDFN package) device. The EEPROM device will be connected to the PS I2C bus (PS bank 500 MIO[24:25]) and operated at VCC of 1.8V. This EEPROM can be used to store system level parameters/data.

## 3.10 I2C 8-Bit I/O Expander

The UltraZed-EG SOM uses the TI **TCA9534PWR** low power I2C 8-bit I/O expander device in the 16-pin TSSOP package for generating various resets and control signals on the UltraZed-EG SOM. The I2C 8-bit I/O expander device is connected to the PS I2C bus (PS bank 500 MIO[24:25]) and operated at VCC of 1.8V. The interrupt output (**INT#**) of the TCA9534 device is connected to the PS MIO[23]. The following table shows how the I/O expander ports will be used.

Note: On power-up all I/O expander ports default to inputs. With the on-board pull-ups on all ports, all output reset signals shown in the following table will be in their inactive state.

| IO Expander Port | Direction | Usage                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0               | Output    | eMMC soft reset                                                                                                                                                                                                                                                                                                                                                                       |

| P1               | Output    | USB 2.0 ULPI PHY soft reset                                                                                                                                                                                                                                                                                                                                                           |

| P2               | Output    | Gigabit Ethernet PHY soft reset                                                                                                                                                                                                                                                                                                                                                       |

| P3               | Output    | Gigabit Ethernet Power-Down                                                                                                                                                                                                                                                                                                                                                           |

| P4               | Input     | 2-channel I2C switch/mux interrupt input                                                                                                                                                                                                                                                                                                                                              |

| P5               | Input     | This port is connected to the <b>PMBus_ALERT_N</b> signal of the UltraZed-EG SOM PMBus regulators and used along with the channel 1 of the I2C 2-channel switch/mux (connected to the PMBus regulator I2C signals) to perform power management on the UltraZed-EG SOM and the Carrier Card. Please refer to the <u>PMBus Interface</u> section of this document for more information. |

| P6               | Output    | 2-channel I2C switch/mux soft reset                                                                                                                                                                                                                                                                                                                                                   |

| P7               | Output    | Active low Carrier Card Reset output ( <b>P7_CC_RST_N</b> ). Please refer to the <u>Carrier Card Reset Output</u> section of this document for more information.                                                                                                                                                                                                                      |

Table 5 – I2C I/O Expander Port Usage

## 3.11 2-Channel I2C Switch/Mux

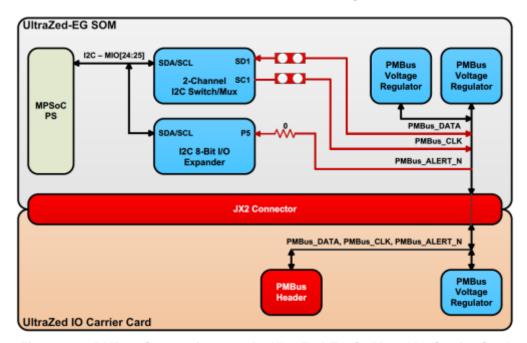

The UltraZed-EG SOM uses a 2-channel I2C switch/mux to expand the PS I2C bus (PS bank 500 MIO[24:25]). The TI **TCA9543APWR** device in the 14-pin TSSOP package is used for this interface. The use of this I2C switch/mux provides a nice isolation so that devices connected to the I2C bus on the UltraZed-EG SOM and the I2C slave devices on the custom Carrier Cards as well as the voltage regulators connected the PMBus I2C are not physically placed on the same I2C bus as shown in Figure 1.

The TCA9543A may also be used for voltage translation, allowing the use of different bus voltages on each SD/SC pair such that 1.8V, 2.5V, or 3.3V devices can communicate with the PS 1.8V I2C MIO pins. This is achieved by using external pull-up resistors to pull the bus up to the desired voltage for the master and each slave channel. The TCA9543A VCC must be connected to the 2.5V rail (please refer to the TCA9543A datasheet for more information).

P6 port of the I2C 8-bit I/O expander can be used to soft reset the 2-channel I2C switch/mux device. The following table shows how each TCA9543A channel will be used.

| I2C Switch Channel                | Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Notes                                                                                                                             |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Master Channel (SDA/SCL/INT)      | This channel is connected to the PS I2C port, MIO[24:25] and operated at 1.8V. The master <b>INT</b> output is connected to the P4 port of the I2C 8-bit I/O expander.                                                                                                                                                                                                                                                                                                                                                                                                   | Pulled-up to 1.8V<br>On the SOM                                                                                                   |

| Slave Channel 0<br>(SD0/SC0/INT0) | This channel is connected to the JX3 connector (CC_SDA, CC_SCL, and CC_INT_N signals) to allow slave I2C devices on the Carrier Card to be virtually placed on the same PS I2C bus (MIO[24:25]) as the I2C devices on the UltraZed-EG SOM so that software can use a single PS I2C core to communicate will all I2C devices in the system. Please refer to the <a href="Carrier Card I2C Interface">Carrier Card I2C Interface</a> section of this document for more information.                                                                                        | Pulled-up to<br>1.8V, 2.5V, or<br>3.3V On the<br>Carrier Card                                                                     |

| Slave Channel 1<br>(SD1/SC1/INT1) | This channel is connected to the PMBus (PMBus_DATA and PMBus_CLK signals) of the UltraZed-EG SOM PMBus voltage regulators and used to control all PMBus voltage regulators on the UltraZed-EG SOM as well as the Carrier Card (the PMBus is connected to the Carrier Card via JX2 connector).  This feature allows the PS to control/monitor the PMBus voltage regulators on the UltraZed-EG SOM as well as the Carrier Card for the purpose of power management and/or measurements. Please refer to the PMBus Interface section of this document for more information. | Pulled-up to 3.3V<br>On the SOM<br>The unused<br>slave channel 1<br>INT1 input must<br>be pulled up to<br>the VCC (2.5V)<br>rail. |

Table 6 - I2C Switch/Mux Channel Usage

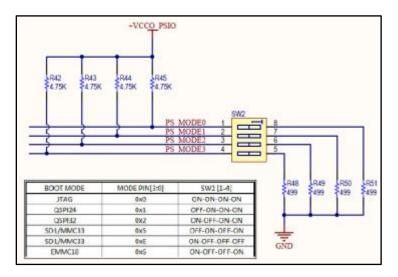

## 3.12 PS Boot Mode Switch

The UltraZed-EG SOM uses a small 4-position DIP switch for the PS Boot Mode pins. This switch is connected to the MODE[0:3] pins of the PS bank 503 and allows users to select the PS primary boot device.

Figure 2 – PS Boot Mode Switch

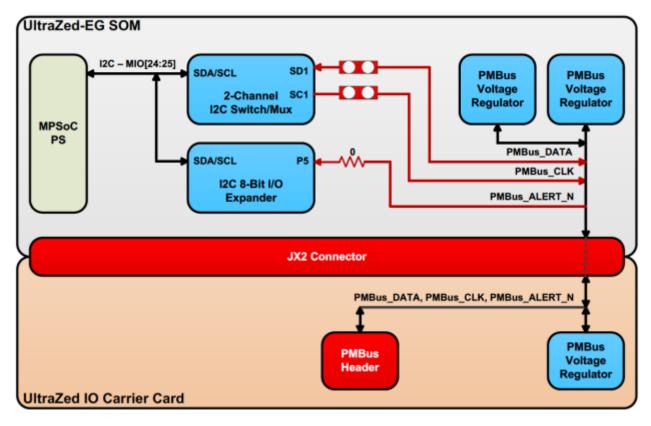

#### 3.13 PMBus Interface

PMBus is used on the UltraZed-EG SOM to program/control/monitor all on-board PMBus voltage regulators. The UltraZed-EG SOM has access to the Carrier Card PMBus header via the JX2 connector (PMBus\_DATA, PMBus\_CLK, and PMBus\_ALERT\_N signals). The Carrier Card PMBus header along with a programming dongle can be used to program all UltraZed-EG SOM PMBus voltage regulators.

An UltraZed-EG custom Carrier Card can provide a PMBus header for programming of all PMBus voltage regulators on the Carrier Card as well as the PMBus voltage regulators on the UltraZed-EG SOM, but it is not required to do so. The PMBus regulators on the UltraZed-EG SOM are preprogrammed prior to shipment. However, if programming of PMBus voltage regulators on a custom Carrier Card is required, the custom Carrier Card must implement the PMBus header.

After the initial programming of all PMBus voltage regulators, the UltraZed-EG SOM can drive the PMBus (via channel 1 of the I2C switch/mux and P5 port of the I2C 8-bit I/O expander) in order to control/monitor the PMBus voltage regulators on the UltraZed-EG SOM for the purpose of power management and/or measurements. If the PMBus is implemented on the custom Carrier Card, the UltraZed-EG SOM PMBus can monitor/control the Carrier Card PMBus voltage regulators as well. If not used, the UltraZed-EG SOM PMBus interface must be left unconnected on custom Carrier Cards so that the UltraZed-EG SOM can still control/monitor its on-board PMBus regulators. The following figure shows how the PMBus is connected on the UltraZed-EG SOM and the Avnet IO Carrier Card.

Figure 3 - UltraZed-EG SOM PMBus Interface

## 3.14 SOM Reset Structure

The following figure shows the reset structure for the MPSoC device and the Carrier Card. The reset operation for the peripherals connected to the MPSoC on the UltraZed-EG SOM will be as follows:

- eMMC Device This device can only be reset via the P0 port of the I2C 8-bit I/O expander.

- USB 2.0 ULPI PHY This device can be reset via PS\_POR\_B, PS\_SRST\_B, or the P1 port of the I2C 8-bit I/O expander.

- Gigabit Ethernet PHY This device can be reset via PS\_POR\_B, PS\_SRST\_B, or the P2 port of the I2C 8-bit I/O expander.

- 2-Channel I2C Switch/Mux Device This device can be reset via PS\_POR\_B,

PS\_SRST\_B, or the P6 port of the I2C 8-bit I/O expander.

Figure 4 - UltraZed-EG SOM Reset Structure

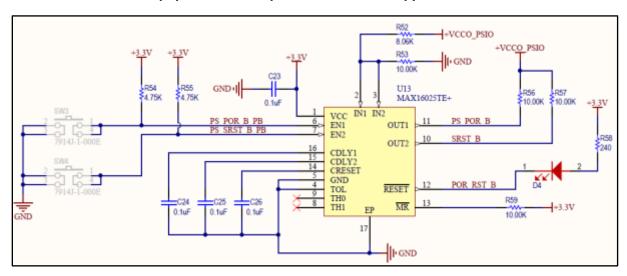

## 3.15 PS Power-On Reset (POR) Circuit

The Power-On Reset (POR) circuit for the MPSoC device is implemented on the UltraZed-EG SOM. This circuit generates the **PS\_POR\_B** as well as the **PS\_SRST\_B** signals. Two small push switches (SW3 and SW4) can be used to manually assert the **PS\_POR\_B** as well as the PS\_SRST\_B signals as shown in the following figure. **The PS\_POR\_B** and the **PS\_SRST\_B** push switches are not populated on the production **SOMs** shipped to customers.

Figure 5 - PS Power-up Reset Circuit

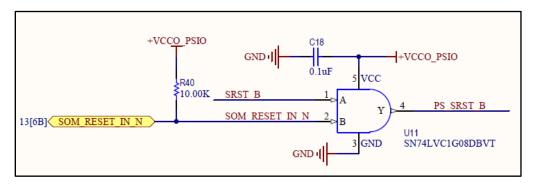

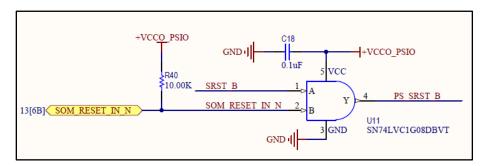

## 3.16 SOM Reset Input

The UltraZed-EG SOM can be reset via an **active low** reset signal from the custom Carrier Card (**SOM\_RESET\_IN\_N**) connected to the JX2 connector. The **SOM\_RESET\_IN\_N** signal can be used to reset the MPSoC device as well as all other device on the UltraZed-EG SOM. The **SOM\_RESET\_IN\_N** signal must be a 1.8V input signal and it is pulled up on the UltraZed-EG SOM. If not used, the **SOM\_RESET\_IN\_N** signal must be left unconnected on the custom Carrier Cards. The SOM\_RESET\_IN\_N signal must have a minimum pulse width of **3xPS\_CLK or 90ns**, required by the UltraZed-EG SOM.

Figure 6 - SOM Input Reset Circuit

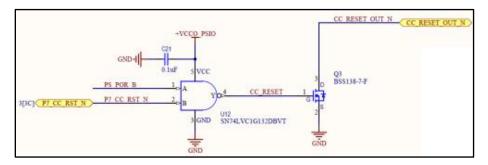

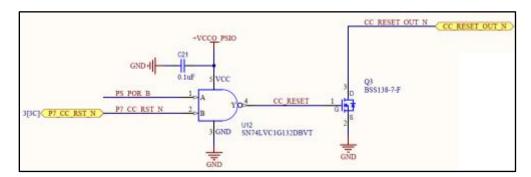

## 3.17 Carrier Card Reset Output

The UltraZed-EG SOM provides an **active low** reset signal to the Carrier Card (CC\_RESET\_OUT\_N) via JX2 connector. The CC\_RESET\_OUT\_N signal can be used to reset any device on the Carrier Card. The CC\_RESET\_OUT\_N signal will be generated by ANDing the PS Power-On Reset (PS\_POR\_B signal) and the P7 port of the I2C 8-bit I/O expander device (P7\_CC\_RST\_N signal) together as shown in the following figure (the below circuit uses a NAND gate along with an inverter to make the CC\_RESET\_OUT\_N signal 1.8V/2.5V/3.3V capable). The CC\_RESET\_OUT\_N signal must be pulled up to 1.8V, 2.5V, or 3.3V on the Carrier Card.

Figure 7 - Carrier Card Output Reset Circuit

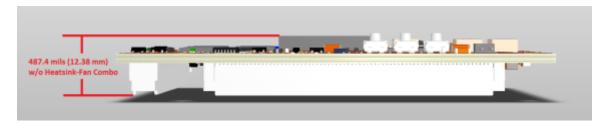

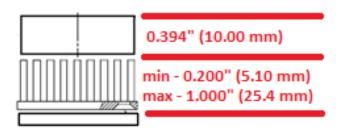

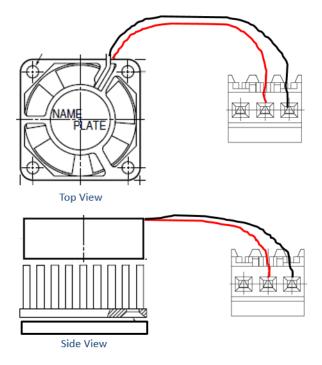

#### 3.18 MPSoC Heat Sink with Fan

The UltraZed-EG SOM uses a heat sink with fan for the MPSoC device. Users can use either a 5V or a 12V fan with the UltraZed-EG SOM heat sink (The UltraZed-EG SOM is shipped with a 5V fan). The fan header will be located on the UltraZed-EG custom Carrier Card and must be designed to match the fan voltage used on the SOM. Please refer to the <u>Carrier Card PCB Design Guidelines</u> section of this document for more information.

## 3.19 Voltage Regulators

Voltage regulators are used on the UltraZed-EG SOM to provide power to all components/interfaces used on the UltraZed-EG SOM. Power for the components/interfaces implemented on the Carrier Card will be supplied by the Carrier Card (these will consist of, but not limited to all the interfaces/components that will utilize the UltraZed-EG SOM PS GTR transceivers, PS MIO bank 501, and/or PL HD/HP banks).

The UltraZed-EG SOM receives an input voltage of 5 – 12V from the custom Carrier Card and generates the voltage rails needed on the UltraZed-EG SOM using two PMBus voltage regulators. The UltraZed-EG SOM power architecture supports all speed grades offered for the ZU3EG-A625 device.

The UltraZed-EG SOM requires the following voltage rails to be supplied by the custom Carrier Cards. Please refer to the <u>Power Requirements</u> and the <u>UltraZed-EG SOM External Interfaces</u> sections of this document for more information.

- 5 12V main input voltage via JX1/JX2 connector

- PS MGTRAVCC (0.85V) via JX3 connector

- PS MGTRAVTT (1.8V) via JX3 connector

- PS MIO bank 501 VCCO (1.8V, 2.5V, or 3.3V) via JX3 connector

- PL HP bank 64 VCCO (1.0V 1.8V) via JX1 connector

- PL HP bank 65 VCCO (1.0V 1.8V) via JX1 connector

- PL HP bank 66 VCCO (1.0V 1.8V) via JX2 connector

- PL HD bank 26 VCCO (1.2V 3.3V) via JX2 connector

- PS VBATT (1.5V) via JX3 connector

## 4 UltraZed-EG SOM External Interfaces

The UltraZed-EG SOM provides sufficient resources to the custom Carrier Cards to implement fully customized systems that meet their application requirements. The UltraZed-EG SOM provides the following external interfaces to the custom Carrier Cards (signal directions are with respect to the UltraZed-EG SOM):

- 26 PS MIO pins (PS MIO bank 501, MIO[26:51])

- 4 PS GTR transceivers

- 4 PS GTR reference clock inputs

- PS JTAG interface

- PL SYSMON interface

- PMBus interface

- Carrier Card I2C interface

- SOM Reset input

- Carrier Card interrupt input

- Carrier Card Reset output

- USB 2.0 connector interface

- Gigabit Ethernet RJ45 connector interface

- 24 PL HD (High Density) I/O pins (1 bank)

- 156 PL HP (High Performance) I/O pins (3 banks)

- SOM PS VBATT input

- SOM Power Good output

- SOM input power

The 4 PS GTR transceivers along with the 4 GTR reference clock inputs available via UltraZed-EG SOM JX3 connector can be used to implement the following interfaces on the custom Carrier Cards:

- USB 3.0 interface

- PCle Endpoint or Root Port interface

- SATA Host interface

- Display Port interface

The 26 PS Multiplexed I/O (MIO) pins available via UltraZed-EG SOM JX3 connector can be used to

- SD card interface

- CAN, UART, I2C, SPI interfaces

- General-purpose I/O (GPIO)

The PL HD and HP general-purpose I/O pins can be used to implement a variety of interfaces on the custom Carrier Cards. Please refer to the Avnet **UltraZed IO Carrier Card Users Guide** on the <a href="https://www.ultrazed.org/product/ultrazed-io-carrier-card">www.ultrazed.org/product/ultrazed-io-carrier-card</a> website for examples of interfaces implemented using the PL HD and HP I/O pins.

The following figure shows the UltraZed-EG SOM external interfaces followed by a brief description of each interface and how to design for it on the custom Carrier Cards.

Figure 8 – UltraZed-EG SOM External Interfaces

| O'mar I N                                                                                                             | # - C D:  | Description                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                                                                                                           | # of Pins | Description                                                                                                                                                                                                                                                                                              |

| MIO[26:51]                                                                                                            | 26        | PS MIO Interface – 26 MIO pins from PS bank 501.                                                                                                                                                                                                                                                         |

| USB_OTG_P,<br>USB_OTG_N,<br>USB_ID,<br>USB_OTG_VBUS,<br>USB_OTG_CPEN                                                  | 5         | <b>USB 2.0 PHY Interface</b> – These pins are used by the custom Carrier Cards to implement a USB 2.0 interface. Please refer to the USB3320 datasheet for AC and DC spec of these signals.                                                                                                              |

| ETH_MD[1:4]_P,<br>ETHMD[1:4]_N,<br>ETH_PHY_LED[0:1]                                                                   | 10        | <b>Gigabit Ethernet PHY Interface</b> – These pins are used by the custom Carrier Cards to implement a Gigabit Ethernet interface. Please refer to the DP83867 datasheet for AC and DC spec of these signals.                                                                                            |

| GTR_TX[0:3]_P,<br>GTR_TX[0:3]_N,<br>GTR_RX[0:3]_P,<br>GTR_RX[0:3]_N,<br>GTR_REFCLK[0:3]_P,<br>GTR_REFCLK[0:3]_N       | 24        | <b>PS GTR Transceivers Interface</b> – These PS transceiver data and clock signals are used by the custom Carrier Cards to implement PCIe, SATA, DisplayPort, and USB 3.0 interfaces. Please refer to the Xilinx DS925 (Zynq UltraScale+ MPSoC datasheet) datasheet for AC and DC spec of these signals. |

| CC_SDA,<br>CC_SCL,<br>CC_INT_N                                                                                        | 3         | Carrier Card I2C Interface – This I2C interface will be used to interface to the custom Carrier Cards I2C slave devices.                                                                                                                                                                                 |

| HP I/O                                                                                                                | 156       | PL HP I/O – These pins are connected to the PL banks 64, 65, and 66. These signals can be used by the custom Carrier Cards as single-ended or differential I/O. Please refer to the Xilinx UG571 and DS925 for more information on the PL High Performance (HP) I/Os.                                    |

| HD I/O                                                                                                                | 24        | <b>PL HD I/O</b> – These pins are connected to the PL bank 26. These signals can be used by the custom Carrier Cards as single-ended or differential input. Please refer to the Xilinx UG571 and DS925 for more information on the PL High Density (HD) I/Os.                                            |

| JTAG_TMS, JTAG_TCK,<br>JTAG_TDI,<br>JTAG_TDO                                                                          | 4         | <b>JTAG Interface</b> – These pins are used to interface to the MPSoC JTAG port and driven by a JTAG cable on the custom Carrier Cards.                                                                                                                                                                  |

| SYSMON_V_P,<br>SYSMON_V_N,<br>SYSMON_DX_P,<br>SYSMON_DX_N                                                             | 4         | <b>SYSMO Interface</b> – Custom Carrier Cards can use these pins to drive low speed analog signals into the PL System Monitor interface. Please refer to the Xilinx UG580 and DS925 for more information on the System Monitor interface.                                                                |

| PMBus_DATA,<br>PMBus_CLK,<br>PMBus_ALERT_N                                                                            | 3         | <b>PMBus Interface</b> – This PMBus I2C interface is used to program and/or monitor the PMBus voltage regulators on the SOM as well as custom Carrier Cards (optional).                                                                                                                                  |

| SOM_RESET_IN_N,<br>CC_RESET_OUT_N                                                                                     | 2         | <b>Reset Signals</b> – These reset signals are used to reset the SOM or the devices on the custom Carrier Cards.                                                                                                                                                                                         |

| VCCO_HP_64                                                                                                            | 3         | PL Bank 64 VCCO – 1.0 – 1.8V sourced by the Carrier Cards.                                                                                                                                                                                                                                               |

| VCCO_HP_65                                                                                                            | 3         | PL Bank 65 VCCO – 1.0 – 1.8V sourced by the Carrier Cards.                                                                                                                                                                                                                                               |

| VCCO_HP_66                                                                                                            | 3         | PL Bank 66 VCCO – 1.0 – 1.8V sourced by the Carrier Cards.                                                                                                                                                                                                                                               |

| VCCO_HD_26                                                                                                            | 3         | PL Bank 26 VCCO – 1.2 – 3.3V sourced by the Carrier Cards.                                                                                                                                                                                                                                               |

| MGTRAVCC                                                                                                              | 3         | <b>PS GTR Core Voltage</b> – 0.85V sourced by the Carrier Cards.                                                                                                                                                                                                                                         |

| MGTRAVTT                                                                                                              | 2         | <b>PS GTR Termination Voltage</b> – 1.8V sourced by the Carrier Cards.                                                                                                                                                                                                                                   |

| VCCO_PSIO_501                                                                                                         | 1         | PS MIO Bank 501 VCCO – 1.8/2.5/3.3V sourced by the Carrier Cards.                                                                                                                                                                                                                                        |

| PS_VBATT                                                                                                              | 1         | <b>PS VBATT Input</b> – 1.5V sourced by the Carrier Cards.                                                                                                                                                                                                                                               |

| MGTRAVCC_Sense,<br>MGTRAVTT_Sense,<br>VCCO_HP_64_Sense,<br>VCCO_HP_65_Sense,<br>VCCO_HP_66_Sense,<br>VCCO_HD_26_Sense | 6         | Voltage Sense Feedback – These output pins are used by the custom Carrier Cards to compensate for the voltage loss across the JX connectors.                                                                                                                                                             |

| SOM_PG_OUT                                                                                                            | 1         | <b>SOM Power Good Output</b> – This signal is used to enable the Carrier Card voltage regulators.                                                                                                                                                                                                        |

| GND                                                                                                                   | 87        | Ground Pins                                                                                                                                                                                                                                                                                              |

| VIN                                                                                                                   | 6         | Main Input Voltage – 5 to 12V DC.                                                                                                                                                                                                                                                                        |

Table 7 – UltraZed-EG SOM External Interface Signals

#### 4.1 PS MIO Interface

The PS MIO interface consists of 26 MIO pins, MIO[26:51] connected to the PS MIO bank 501. These MIO pins are routed to the JX3 connector and are available to the custom Carrier Cards. The PS bank 501 I/O is operated at 1.8V, 2.5V, or 3.3V provided by the custom Carrier Cards via JX3 connector. This full bank of MIO pins can be used on a custom Carrier Card to implement various interfaces (please refer to the Xilinx UG1085 for more information on the PS MIO available interfaces). On the Avnet UltraZed IO Carrier Card, PS MIO bank 501 is operated at 3.3V and used to implement the following interfaces:

- microSD card

- Dual USB-UART ports

- PS PMOD header

- PS user LED and push switch

- Display Port auxiliary interface

The following table shows the UltraZed-EG SOM PS MIO[26:51] pins available on the JX3 connector.

| Signal Name | JX3 Pin # |     | Signal Name |

|-------------|-----------|-----|-------------|

| MIO[26]     | 69        | 70  | MIO[27]     |

| MIO[28]     | 71        | 72  | MIO[29]     |

| MIO[30]     | 73        | 74  | MIO[31]     |

| MIO[32]     | 77        | 78  | MIO[33]     |

| MIO[34]     | 79        | 80  | MIO[35]     |

| MIO[36]     | 81        | 82  | MIO[37]     |

| MIO[38]     | 85        | 86  | MIO[39]     |

| MIO[40]     | 87        | 88  | MIO[41]     |

| MIO[42]     | 89        | 90  | MIO[43]     |

| MIO[44]     | 93        | 94  | MIO[45]     |

| MIO[46]     | 95        | 96  | MIO[47]     |

| MIO[48]     | 97        | 98  | MIO[49]     |

| MIO[50]     | 99        | 100 | MIO[51]     |

Table 8 - PS MIO Bank 501 Pin Assignments

Please refer to pages 3, 5, 10, 11, and 12 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on the PS MIO Interfaces implemented on the Avnet IO Carrier Card.

## 4.2 PS USB 2.0 Connector Interface

The UltraZed-EG SOM USB 2.0 ULPI PHY connector side interface can be used on a custom Carrier Card to implement a USB 2.0 interface using a USB/microUSB connector. If so desired, this USB 2.0 ULPI PHY connector side interface along with a SOM PS GTR transceiver (available on the JX3 connector) can be used to implement a USB 2.0/3.0 interface via a single USB 2.0/3.0 connector. The USB 2.0/3.0 interface can be designed to support Host/OTG or Device mode. The following table shows the UltraZed-EG SOM USB 2.0 ULPI PHY connector side interface pins available on the JX3 connector.

| Signal Name | JX3 Pin # |    | Signal Name  |

|-------------|-----------|----|--------------|

| USB_OTG_P   | 45        | 48 | USB_OTG_CPEN |

| USB_OTG_N   | 47        | 50 | USB_OTG_VBUS |

| USB_ID      | 51        |    |              |

Table 9 – PS USB 2.0 Connector Interface Pin Assignments

Please refer to page 5 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on the RJ45 connector Interface implemented on the Avnet IO Carrier Card.

## 4.3 PS RJ45 Connector Interface

The UltraZed-EG SOM Gigabit Ethernet PHY connector side interface along with an RJ45 connector on the custom Carrier Card can be used to implement a single Gigabit Ethernet port. The following table shows the UltraZed-EG SOM Gigabit Ethernet PHY connector side interface pins available on the JX3 connector.

| Signal Name  | JX3 Pin # |    | Signal Name  |

|--------------|-----------|----|--------------|

| ETH_PHY_LED0 | 53        | 70 | ETH_PHY_LED1 |

| ETH_MD1_P    | 57        | 72 | ETH_MD2_P    |

| ETH_MD1_N    | 59        | 74 | ETH_MD2_N    |

| ETH_MD3_P    | 63        | 78 | ETH_MD4_P    |

| ETH_MD3_N    | 65        | 80 | ETH_MD4_N    |

Table 10 - PS RJ45 Connector Interface Pin Assignments

Please refer to page 5 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on the RJ45 connector Interface implemented on the Avnet IO Carrier Card.

#### 4.4 PS GTR Transceiver Interface

The UltraZed-EG SOM provides 4 PS GTR transceivers along with 4 GTR reference clock inputs to the custom Carrier Cards via the JX3 connector. These 4 transceivers can be used on a custom Carrier Card to implement USB 3.0, Display Port, SATA host, and PCle interfaces. Please refer to the UG1085 (Zynq UltraScale+ Technical Reference Manual) for more information on how each GTR transceiver can be used in a design.

The GTR transceiver power (0.85V and 1.8V rails) must be supplied by the custom Carrier Card via JX3 connector. Please refer to the **Power Requirements** section of this document for more information. The following table shows the UltraZed-EG SOM PS GTR and GTR reference clock input pins available on the JX3 connector.

| Signal Name   | JX3 | Pin # | Signal Name   |

|---------------|-----|-------|---------------|

| GTR_TX3_P     | 1   | 4     | GTR_RX3_P     |

| GTR_TX3_N     | 3   | 6     | GTR_RX3_N     |

| GTR_TX2_P     | 7   | 10    | GTR_RX2_P     |

| GTR_TX2_N     | 9   | 12    | GTR_RX2_N     |

| GTR_TX1_P     | 13  | 18    | GTR_RX1_P     |

| GTR_TX1_N     | 15  | 20    | GTR_RX1_N     |

| GTR_TX0_P     | 21  | 26    | GTR_RX0_P     |

| GTR_TX0_N     | 23  | 28    | GTR_RX0_N     |

| GTR_REFCLK3_P | 27  | 32    | GTR_REFCLK2_P |

| GTR_REFCLK3_N | 29  | 34    | GTR_REFCLK2_N |

| GTR_REFCLK1_P | 33  | 38    | GTR_REFCLK0_P |

| GTR_REFCLK1_N | 35  | 40    | GTR_REFCLK0_N |

Table 11 - PS GTR Interface Pin Assignments

Please refer to pages 3, 4, 5, and 16 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how PS GTR interfaces are implemented on the Avnet IO Carrier Card.

#### 4.5 PL HD I/O Pins

The PL HD I/O interface consists of 24 HD (High Density) I/O pins connected to the Zynq UltraScale+ MPSoC bank 26. These pins are routed to the JX2 connector and can be used on custom Carrier Cards to implement various interfaces. The PL HD bank I/O pins can be operated at 1.2V – 3.3V. The VCCO voltage for the PL HD bank must be supplied by the custom Carrier Cards via JX2 connector. Please refer to the <a href="Power Requirements">Power Requirements</a> section of this document for more information.

**Note:** The Zynq UltraScale+ MPSoC HD banks do not support differential output (single-ended I/O or differential input with external termination only).

Please refer to page 6 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how PL HD I/O pins are used on the Avnet IO Carrier Card.

## 4.6 PL HP I/O Pins

The PL HP I/O interface consists of 156 HP (High Performance) I/O pins connected to the Zynq UltraScale+ MPSoC banks 64, 65, and 66. These pins are routed to the JX1/JX2 connectors (as 72 differential pairs and 12 single-ended signals) and can be used on custom Carrier Cards to implement various interfaces. The PL HP banks I/O pins will be operated at 1.0V – 1.8V. The VCCO voltages for the PL HP banks must be supplied by the custom Carrier Cards via JX1/JX2 connectors. Please refer to the Power Requirements section of this document for more information.

Please refer to pages 4, 7, 8, 11, and 12 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how PL HP I/O pins are used on the Avnet IO Carrier Card.

#### 4.7 PL SYSMON Interface

The PL SYSMON interface is connected to the bank 0 of the Zynq UltraScale+ MPSoC and consists of **VP**, **VN**, **DXP**, and **DXN** pins. These pins are routed to the JX2 connector and can be used on custom Carrier Cards to implement low speed analog interface. The SYSMON supply voltages, VCCADC and VREF are provided on the UltraZed-EG SOM. If not used, the SYSMON signals can be left unconnected on the custom Carrier Card. The following table shows the UltraZed-EG SOM SYSMON interface pins available on the JX2 connector.

| Signal Name | JX2 Pin # |   | Signal Name |

|-------------|-----------|---|-------------|

| SYSMON_V_N  | 1         | 2 | SYSMON_DX_N |

| SYSMON V P  | 3         | 4 | SYSMON DX P |

Table 12 - PL SYSMON Interface Pin Assignments

Please refer to page 13 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how PL SYSMON pins are used on the Avnet IO Carrier Card.

## 4.8 SOM Reset Input

The UltraZed-EG SOM can be reset via an active low reset signal from the Carrier Card (SOM\_RESET\_IN\_N) connected to the JX2 connector. The SOM\_RESET\_IN\_N signal can be used to reset the MPSoC device as well as all other device on the UltraZed-EG SOM. The SOM\_RESET\_IN\_N is a 1.8V signal and it is pulled up to the 1.8V rail on the UltraZed-EG SOM. The SOM\_RESET\_IN\_N signal must have a minimum pulse width of 3xPS\_CLK or 90ns, required by the UltraZed-EG SOM.

Figure 9 - SOM Input Reset Circuit on the UltraZed-EG SOM

Please refer to page 11 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how SOM\_RESET\_IN\_N signal is generated on the Avnet IO Carrier Card.

## 4.9 Carrier Card Reset Output

The UltraZed-EG SOM provides an **active low** reset signal to the Carrier Card (**CC\_RESET\_OUT\_N**) via JX2 connector. The **CC\_RESET\_OUT\_N** signal can be used to reset any device on the Carrier Card. The **CC\_RESET\_OUT\_N** signal must be pulled up to 1.8V, 2.5V, or 3.3V on the custom Carrier Card.

Figure 10 - Carrier Card Output Reset Circuit on the UltraZed-EG SOM

Please refer to page 15 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how CC\_RESET\_OUT\_N signals is used on the Avnet IO Carrier Card.

## 4.10 Carrier Card I2C Interface

The UltraZed-EG SOM provides a master I2C bus (CC\_SDA, CC\_SCL, and CC\_INT\_N) to the Carrier Card via the JX3 connector so that software can communicate with all I2C devices on the UltraZed-EG SOM as well as the slave I2C devices on the Carrier Card using a single I2C interface. The CC\_SDA, CC\_SCL, and CC\_INT\_N pins must be pulled up to the 1.8V, 2.5V, or 3.3V on the Carrier Card.

The Carrier Card I2C interface is connected to the channel 0 of the I2C 2-channel switch/mux device on the UltraZed-EG SOM. Carrier Cards can drive the INT0 of the channel 0 via CC\_INT\_N, if they so desire. The CC\_INT\_N signal is not specific to the I2C interface and can be used as a general-purpose interrupt from Carrie Cards to the UltraZed-EG SOM. If not used, the CC\_INT\_N signal must be pulled up to 1.8V, 2.5V, or 3.3V on the Carrier Card. Since channel 0 I2C bus is dedicated to the Carrier Card, I2C devices with any address can reside on this bus without conflicting with the I2C devices on the UltraZed-EG SOM. The following table shows the UltraZed-EG SOM Carrier Card I2C interface pins available on the JX3 connector.

| Signal Name | JX3 Pin # |    | Signal Name |

|-------------|-----------|----|-------------|

| CC_SDA      | 41 44     |    | CC_SCL      |

|             |           | 68 | CC INT N    |

Table 13 - Carrier Card I2C Interface Pin Assignments

Please refer to pages 4 and 5 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how Carrier Card I2C is used on the Avnet IO Carrier Card.

## 4.11 Ethernet MAC ID

A MAC Address device such as the Microchip **24AA025E48T-I/OT** device can be used on the custom Carrier Card. This device can be connected to the Carrier Card I2C interface (**CC\_SDA** and **CC\_SCL**).

Please refer to page 5 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how the MAC ID is implemented on the Avnet IO Carrier Card.

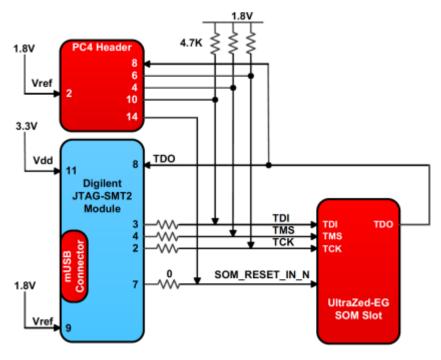

## 4.12 JTAG Interface

Custom Carrier Cards must provide the JTAG interface to the UltraZed-EG SOM via JX1 connector. Carrier Cards can implement the JTAG interface using a JTAG header such as the Xilinx PC4 header, a USB-JTAG module such as the Digilent SMT2 module, or designing the JTAG interface using chip-down method on the Carrier Card. The JTAG interface on the custom Carrier Cards must be driven with 1.8V I/O standard.

The Avnet UltraZed IO Carrier Card utilizes the Digilent SMT2 USB-JTAG module to interface to the UltraZed-EG SOM JTAG port. The Digilent USB-JTAG module VREF pin is connected to the 1.8V rail on the UltraZed IO Carrier Card to provide 1.8V I/O on all JTAG signals. The following figure shows the JTAG interface on the Avnet UltraZed IO Carrier Card.

Figure 11 - IO Carrier Card JTAG Interface

The following table shows the UltraZed-EG SOM JTAG pins available on the JX1 connector.

| ZU3EG Signal Name | JX1 | Pin# | ZU3EG Signal Name |

|-------------------|-----|------|-------------------|

| JTAG_TCK          | 1   | 2    | JTAG_TMS          |

| JTAG TDO          | 3   | 4    | JTAG TDI          |

Table 14 - PS JTAG Interface Pin Assignments

Please refer to page 11 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on JTAG interface on the Avnet IO Carrier Card.

## 4.13 PMBus Interface

PMBus is used on the UltraZed-EG SOM to program/control/monitor all on-board PMBus voltage regulators. The UltraZed-EG SOM has access to the Carrier Card PMBus header via the JX2 connector (**PMBus\_DATA**, **PMBus\_CLK**, and **PMBus\_ALERT\_N** signals). The Carrier Card PMBus header along with a programming dongle can be used to program all UltraZed-EG SOM PMBus voltage regulators.

An UltraZed-EG custom Carrier Card can provide a PMBus header for programming of all PMBus voltage regulators on the Carrier Card as well as the PMBus voltage regulators on the UltraZed-EG SOM, but it is not required to do so. The PMBus regulators on the UltraZed-EG SOM are preprogrammed prior to shipment. However, if programming of PMBus voltage regulators on a custom Carrier Card is required, the custom Carrier Card must implement the PMBus header.

After the initial programming of all PMBus voltage regulators, the UltraZed-EG SOM can drive the PMBus (via channel 1 of the I2C switch/mux and P5 port of the I2C 8-bit I/O expander) in order to control/monitor the PMBus voltage regulators on the UltraZed-EG SOM for the purpose of power management and/or measurements. If the PMBus is implemented on the custom Carrier Card, the UltraZed-EG SOM PMBus can monitor/control the Carrier Card PMBus voltage regulators as well. If not used, the UltraZed-EG SOM PMBus interface must be left unconnected on custom Carrier Cards so that the UltraZed-EG SOM can still control/monitor its on-board PMBus regulators. The following figure shows how the PMBus is connected on the UltraZed-EG SOM and the Avnet IO Carrier Card.

| Signal Name   | JX2 Pin # |    | ZU3EG Signal Name |

|---------------|-----------|----|-------------------|

| PMBus_SDA     | 11        | 12 | PMBus_SCL         |

| PMBus_ALERT_N | 35        |    |                   |

Table 15 - PMBus Interface Pin Assignments

Figure 12 - PMBus Connections on the UltraZed-EG SOM and IO Carrier Card

Please refer to page 13 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how the PMBus interface is implemented on the Avnet IO Carrier Card.

## 4.14 Power Requirements

The UltraZed-EG SOM requires the following rails to be supplied by the Carrier Card. In return, the UltraZed-EG SOM will provide a voltage sense feedback for each rail (with the exception of the 5 – 12V input voltage and the PS MIO bank 501 VCCO) to the Carrier Card via JX connectors (please refer to section 5 of this document for the JX1, JX2, and JX3 detail pinout information). The voltage sense feedback for each rail can be used by the regulator on the Carrier Card to compensate for the voltage loss across the JX connectors. Please refer to the DS925 (Zynq UltraScale+ MPSoC datasheet) for percent variation on all the following voltage rails when designing the power system for the custom Carrier Card. The custom Carrier Cards are required to supply the following rails to the UltraZed-EG SOM:

- 5 12V main input voltage via JX1/JX2 connectors

- PS MGTRAVCC (0.85V) via JX3 connector

- PS MGTRAVTT (1.8V) via JX3 connector

- PS MIO bank 501 VCCO (1.8V, 2.5V, or 3.3V) via JX3 connector

- PL HP bank 64 VCCO (1.0V 1.8V) via JX1 connector

- PL HP bank 65 VCCO (1.0V 1.8V) via JX1 connector

- PL HP bank 66 VCCO (1.0V 1.8V) via JX2 connector

- PL HD bank 26 VCCO (1.2V 3.3V) via JX2 connector

- PS VBATT (1.5V) via JX3 connector

| Voltage Rail Name | Voltage Value       | Current Requirement     | Voltage Sense Feedback |

|-------------------|---------------------|-------------------------|------------------------|

| VIN               | 5 – 12V             | 3.6A @ 5V or 1.5A @ 12V | NA                     |

| MGTRAVCC          | 0.85V               | 1A                      | MGTRAVCC_Sense         |

| MGTRAVTT          | 1.8V                | 1A                      | MGTRAVTT_Sense         |

| VCCO_PSIO_501     | 1.8V, 2.5V, or 3.3V | 0.5A                    | NA                     |

| VCCO_HP_64        | 1.0V – 1.8V         | 1A                      | VCCO_HP_64_Sense       |

| VCCO_HP_65        | 1.0V – 1.8V         | 1A                      | VCCO_HP_65_Sense       |

| VCCO_HP_66        | 1.0V – 1.8V         | 1A                      | VCCO_HP_66_Sense       |

| VCCO_HD_26        | 1.2V - 3.3V         | 0.5A                    | VCCO_HD_26_Sense       |

| PS_VBATT          | 1.5V                | 250nA                   | NA                     |

Table 16 - UltraZed-EG SOM Power Requirements

Some of the above voltage rails can be combined to reduce the cost of power supply design on the custom Carrier Card. The MGTRAVCC and MGTRAVTT analog voltage rails should not be combined with any VCCO rails.

On the Avnet UltraZed IO Carrier Card, all PL HP bank VCCOs are driven with a single 1.8V supply. The PL HD bank VCCO and PS MIO bank 501 VCCO are driven with a single 3.3V supply. The following lists the regulated voltage rails generated by a single PMBus voltage regulator on the UltraZed IO Carrier Card for the UltraZed-EG SOM.

- 0.85V for the MGTRAVCC via JX3

- 1.8V for the MGTRAVTT via JX3

- 1.8V for all PL HP banks via JX1/JX2

- 3.3V for the PL HD bank and PS MIO bank 501 via JX2/JX3

## 4.15 Power Sequencing

Proper power sequencing is needed for the following rails supplied to the UltraZed-EG SOM by the Carrier Cards:

- PS MGTRAVCC

- PS MGTRAVTT

- PS MIO bank 501 VCCO

- PL HP bank 64 VCCO

- PL HP bank 65 VCCO

- PL HP bank 66 VCCO

- PL HD bank 26 VCCO

The **SOM\_PG\_OUT** signal from the UltraZed-EG SOM (3.3V signal, connected to the JX2 connector) must be used to assist in power sequencing. The Carrier Card voltage regulator(s) should not be turned ON until the **SOM\_PG\_OUT** signal is asserted.

In order to boot from a device on the custom Carrier Card (such as booting from the microSD/SD Card), all power rails on the custom Carrier Card must be stable within 300ms of the SOM\_PG\_OUT assertion. This will ensure all custom Carrier Card power rails are up and stable before the PS\_POR\_B signal is de-asserted and the MPSoC boot execution is initiated on the UltraZed-EG SOM. The power rails on the Avnet IO Carrier Card are up and stable less than 100ms from the SOM\_PG\_OUT assertion.

Please refer to page 14 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how the SOM PG OUT is used on the Avnet IO Carrier Card.

Once the **SOM\_PG\_OUT** signal is asserted, the Carrier Card must turn on the above voltage rails in the following sequence (the reverse sequence must be maintained on turn off):

- 1. PS MGTRAVCC rail followed by the PS MGTRAVTT rail.

- 2. PS bank 501 and PL banks 26, 64, 65, and 66 VCCO in any sequence before or after the MGTRAVCC/ MGTRAVTT rails.

## 4.16 Power Estimation Using XPE

Xilinx Power Estimator (XPE) should be used to generate worst case power estimations for selecting power devices for the I/O banks. The Xilinx Power Estimator (XPE) spreadsheet is available on Xilinx' website that can help you get started with your own power estimation. You may download this file and add or modify your desired PL utilization to provide a worst case estimation for your own VCCO supplies.

## 4.17 MPSoC Heat Sink with Fan

The UltraZed-EG SOM uses a heat sink with fan for the MPSoC device. Users can use either a 5V or a 12V fan with the UltraZed-EG SOM heat sink (The UltraZed-EG SOM is shipped with a 5V fan). The fan header will be located on the UltraZed-EG custom Carrier Card and must be designed to match the fan voltage used on the SOM. Please refer to the <u>Carrier Card PCB Design Guidelines</u> section of this document for more information.

Please refer to page 15 of the Avnet UltraZed IO Carrier Card schematic at the end of this document for more information on how the Fan Header is implemented on the Avnet IO Carrier Card.

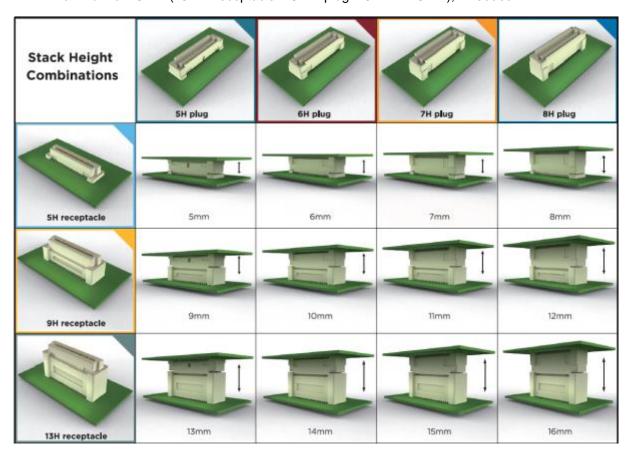

## 5 UltraZed-EG SOM JX Micro Connectors

The UltraZed-EG SOM utilizes 3 micro headers to provide connections to the Carrier Card. TE 0.8mm FH (Free Height) connectors are used to implement the UltraZed-EG SOM to the Carrier Card connections. The UltraZed-EG SOM uses a 100-pin (JX3), and two 140-pin (JX1 and JX2) plug connectors. These connectors carry the following signals and power/ground pins (signal directions are with respect to the UltraZed-EG SOM):

- JX1 Connector (140-pin Plug, TE part number: 2-5177986-6)

- JTAG pins (JTAG TMS, JTAG TCK, JTAG TDI, and JTAG TDO)

- 42 differential HP I/O pairs (JX1\_HP\_DP)

- 6 single ended signals (JX1 HP SE)