# Renesas RA2E1 Group

User's Manual: Hardware

32-Bit MCU Renesas Advanced (RA) Family Renesas RA2 Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

#### **Notice**

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. Renesas Electronics disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, or information.

- Renesas Electronics hereby expressly disclaims any warranties against and liability for infringement or any other claims involving patents, copyrights, or other intellectual property rights of third parties, by or arising from the use of Renesas Electronics products or technical information described in this document, including but not limited to, the product data, drawings, charts, programs, algorithms, and application examples.

- 3. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others

- 4. You shall be responsible for determining what licenses are required from any third parties, and obtaining such licenses for the lawful import, export, manufacture, sales, utilization, distribution or other disposal of any products incorporating Renesas Electronics products, if required.

- 5. You shall not alter, modify, copy, or reverse engineer any Renesas Electronics product, whether in whole or in part. Renesas Electronics disclaims any and all liability for any losses or damages incurred by you or third parties arising from such alteration, modification, copying or reverse engineering.

- Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The intended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; industrial robots; etc.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control (traffic lights); large-scale communication equipment; key financial terminal systems; safety control equipment; etc.

Unless expressly designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not intended or authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems; surgical implantations; etc.), or may cause serious property damage (space system; undersea repeaters; nuclear power control systems; aircraft control systems; key plant systems; military equipment; etc.). Renesas Electronics disclaims any and all liability for any damages or losses incurred by you or any third parties arising from the use of any Renesas Electronics product that is inconsistent with any Renesas Electronics data sheet, user's manual or other Renesas Electronics document.

- 7. No semiconductor product is absolutely secure. Notwithstanding any security measures or features that may be implemented in Renesas Electronics hardware or software products, Renesas Electronics shall have absolutely no liability arising out of any vulnerability or security breach, including but not limited to any unauthorized access to or use of a Renesas Electronics product or a system that uses a Renesas Electronics product. RENESAS ELECTRONICS DOES NOT WARRANT OR GUARANTEE THAT RENESAS ELECTRONICS PRODUCTS, OR ANY SYSTEMS CREATED USING RENESAS ELECTRONICS PRODUCTS WILL BE INVULNERABLE OR FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION ("Vulnerability Issues"). RENESAS ELECTRONICS DISCLAIMS ANY AND ALL RESPONSIBILITY OR LIABILITY ARISING FROM OR RELATED TO ANY VULNERABILITY ISSUES. FURTHERMORE, TO THE EXTENT PERMITTED BY APPLICABLE LAW, RENESAS ELECTRONICS DISCLAIMS ANY AND ALL WARRANTIES, EXPRESS OR IMPLIED, WITH RESPECT TO THIS DOCUMENT AND ANY RELATED OR ACCOMPANYING SOFTWARE OR HARDWARE, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE.

- 8. When using Renesas Electronics products, refer to the latest product information (data sheets, user's manuals, application notes, "General Notes for Handling and Using Semiconductor Devices" in the reliability handbook, etc.), and ensure that usage conditions are within the ranges specified by Renesas Electronics with respect to maximum ratings, operating power supply voltage range, heat dissipation characteristics, installation, etc. Renesas Electronics disclaims any and all liability for any malfunctions, failure or accident arising out of the use of Renesas Electronics products outside of such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of Renesas Electronics products, semiconductor products have specific characteristics, such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Unless designated as a high reliability product or a product for harsh environments in a Renesas Electronics data sheet or other Renesas Electronics document, Renesas Electronics products are not subject to radiation resistance design. You are responsible for implementing safety measures to guard against the possibility of bodily injury, injury or damage caused by fire, and/or danger to the public in the event of a failure or malfunction of Renesas Electronics products, such as safety design for hardware and software, including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult and impractical, you are responsible for evaluating the safety of the final products or systems manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. You are responsible for carefully and sufficiently investigating applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive, and using Renesas Electronics products in compliance with all these applicable laws and regulations. Renesas Electronics disclaims any and all liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. Renesas Electronics products and technologies shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You shall comply with any applicable export control laws and regulations promulgated and administered by the governments of any countries asserting jurisdiction over the parties or transactions.

- 12. It is the responsibility of the buyer or distributor of Renesas Electronics products, or any other party who distributes, disposes of, or otherwise sells or transfers the product to a third party, to notify such third party in advance of the contents and conditions set forth in this document.

- 13. This document shall not be reprinted, reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 14. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products.

- (Note1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its directly or indirectly controlled subsidiaries.

- (Note2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

(Rev.5.0-1 October 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <a href="https://www.renesas.com/contact/">www.renesas.com/contact/</a>

## General Precautions in the Handling of Microprocessing Unit and Microcontroller Unit Products

The following usage notes are applicable to all Microprocessing unit and Microcontroller unit products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

- 1. Precaution against Electrostatic Discharge (ESD)

- A strong electrical field, when exposed to a CMOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop the generation of static electricity as much as possible, and quickly dissipate it when it occurs. Environmental control must be adequate. When it is dry, a humidifier should be used. This is recommended to avoid using insulators that can easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors must be grounded. The operator must also be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions must be taken for printed circuit boards with mounted semiconductor devices.

- 2. Processing at power-on

- The state of the product is undefined at the time when power is supplied. The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the time when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the time when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the time when power is supplied until the power reaches the level at which resetting is specified.

- 3. Input of signal during power-off state

- Do not input signals or an I/O pull-up power supply while the device is powered off. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Follow the guideline for input signal during power-off state as described in your product documentation.

- 4. Handling of unused pins

- Handle unused pins in accordance with the directions given under handling of unused pins in the manual. The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of the LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible

- 5. Clock signals

- After applying a reset, only release the reset line after the operating clock signal becomes stable. When switching the clock signal during program execution, wait until the target clock signal is stabilized. When the clock signal is generated with an external resonator or from an external oscillator during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Additionally, when switching to a clock signal produced with an external resonator or by an external oscillator while program execution is in progress, wait until the target clock signal is stable.

- 6. Voltage application waveform at input pin

- Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.) due to noise, for example, the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{IL}$  (Max.) and  $V_{IH}$  (Min.).

- 7. Prohibition of access to reserved addresses

- Access to reserved addresses is prohibited. The reserved addresses are provided for possible future expansion of functions. Do not access these addresses as the correct operation of the LSI is not guaranteed.

- 8. Differences between products

- Before changing from one product to another, for example to a product with a different part number, confirm that the change will not lead to problems. The characteristics of a microprocessing unit or microcontroller unit products in the same group but having a different part number might differ in terms of internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

## **Preface**

### 1. About this document

This manual is generally organized into an overview of the product, descriptions of the CPU, system control functions, peripheral functions, electrical characteristics, and usage notes. This manual describes the product specification of the microcontroller (MCU) superset. Depending on your product, some pins, registers, or functions might not exist. Address space that store unavailable registers are reserved.

#### 2. Audience

This manual is written for system designers who are designing and programming applications using the Renesas Microcontroller. The user is expected to have basic knowledge of electrical circuits, logic circuits, and the MCU.

#### 3. Renesas Publications

Renesas provides the following documents. Before using any of these documents, visit www.renesas.com for the most up-to-date version of the document.

| Component               | Document Type                    | Description                                                                                                                                            |  |

|-------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Microcontrollers        | Data sheet                       | Features, overview, and electrical characteristics of the MCU                                                                                          |  |

|                         | User's Manual: Hardware          | MCU specifications such as pin assignments, memory maps, peripheral functions, electrical characteristics, timing diagrams, and operation descriptions |  |

|                         | Application Notes                | Technical notes, board design guidelines, and software migration information                                                                           |  |

|                         | Technical Update (TU)            | Preliminary reports on product specifications such as restriction and errata                                                                           |  |

| Software                | User's Manual: Software          | API reference and programming information                                                                                                              |  |

|                         | Application Notes                | Project files, guidelines for software programming, and application examples to develop embedded software applications                                 |  |

| Tools & Kits, Solutions | User's Manual: Development Tools | User's manual and quick start guide for developing embedded                                                                                            |  |

|                         | User's Manual: Software          | software applications with Development Kits (DK), Starter Kits (SK), Promotion Kits (PK), Product Examples (PE), and Application                       |  |

|                         | Quick Start Guide                | Examples (AE)                                                                                                                                          |  |

|                         | Application Notes                | Project files, guidelines for software programming, and application examples to develop embedded software applications                                 |  |

## 4. Numbering Notation

The following numbering notation is used throughout this manual:

| Example | Description                                                                                                                                                       |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 011b    | Binary number. For example, the binary equivalent of the number 3 is 011b.                                                                                        |

| 0x1F    | Hexadecimal number. For example, the hexadecimal equivalent of the number 31 is described 0x1F. In some cases, a hexadecimal number is shown with the suffix "h". |

| 1234    | Decimal number. A decimal number is followed by this symbol only when the possibility of confusion exists. Decimal numbers are generally shown without a suffix.  |

## 5. Typographic Notation

The following typographic notation is used throughout this manual:

| Example            | Description                                                                                                                          |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| WDT.WDTRCR.RSTIRQS | Periods separated a function module symbol (WDT), register symbol (WDTRCR), and bit field symbol (RSTIRQS).                          |

| WDT.WDTRCR         | A period separated a function module symbol (WDT) and register symbol (WDTRCR).                                                      |

| WDTRCR.RSTIRQS     | A period separated a register symbol (WDTRCR) and bit field symbol (RSTIRQS).                                                        |

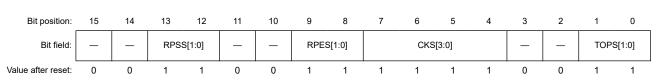

| CKS[3:0]           | Numbers in brackets expresses a bit number. For example, CKS[3:0] occupies bits 3 to 0 of the WDT Control Register (WDTCR) register. |

## 6. Unit and Unit Prefix

The following units and unit prefixes are sometimes misleading. Those unit prefixes are described throughout this manual with the following meaning:

| Symbol | Name         | Description                                                                                                                               |

|--------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| b      | Binary Digit | Single 0 or 1                                                                                                                             |

| В      | Byte         | This unit is generally used for memory specification of the MCU and address space.                                                        |

| k      | kilo-        | $1000 = 10^3$ . k is also used to denote 1024 ( $2^{10}$ ) but this unit prefix is used to denote 1000 ( $10^3$ ) throughout this manual. |

| К      | Kilo-        | $1024 = 2^{10}$ . This unit prefix is used to denote 1024 (2 <sup>10</sup> ) not 1000 (10 <sup>3</sup> ) throughout this manual.          |

## 7. Special Terms

The following terms have special meanings.

| Term | Description                                                       |

|------|-------------------------------------------------------------------|

| NC   | Not connected pin. NC means that pin is not connected to the MCU. |

| Hi-Z | High impedance.                                                   |

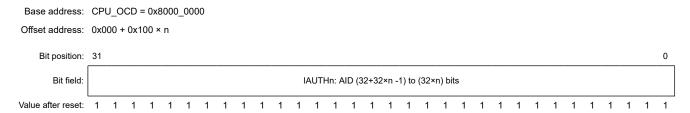

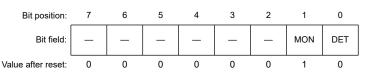

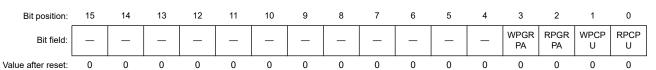

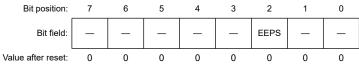

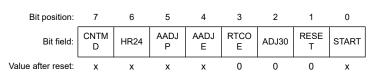

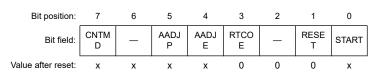

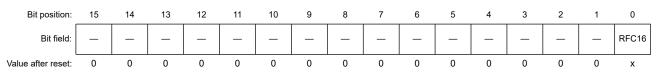

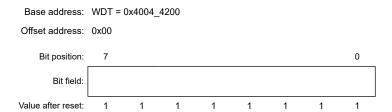

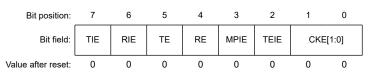

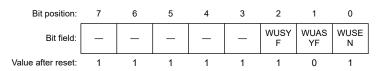

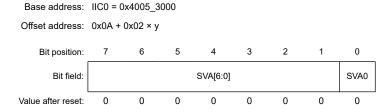

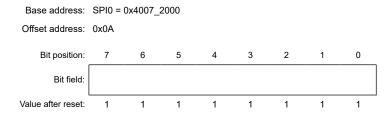

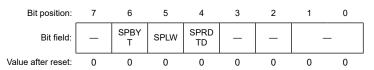

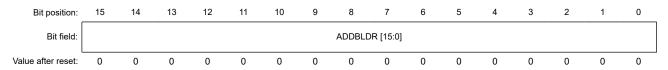

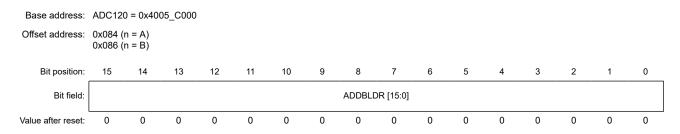

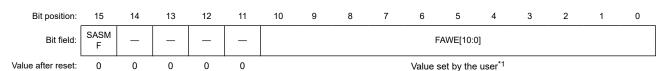

### 8. Register Description

Each register description includes both a register diagram that shows the bit assignments and a register bit table that describes the content of each bit. The example of symbols used in these tables are described in the sections that follow. The following is an example of a register description and associated bit field definition.

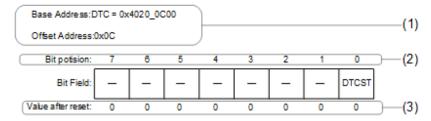

#### XX.X.X DTCST : DTC Module Start Register

|     | (4)    | (5)                                                    | (6) |

|-----|--------|--------------------------------------------------------|-----|

| Bit | Symbol | Function                                               | R/W |

| 0   | DTCST  | DTC Module Start 0:DTC module stop                     | R/W |

|     |        | 1:DTC module start                                     |     |

| 7:1 | _      | These bits are read as 0. The write value should be 0. | R/W |

#### (1) Function module symbol, register symbol, and address assignment

Function module symbol, register symbol, and address assignment of this register are generally expressed. Base Address and Offset Address mean DTC Module Start Register (DTCST) of Data Transfer Controller (DTC) is assigned to address 0x4020 0C00.

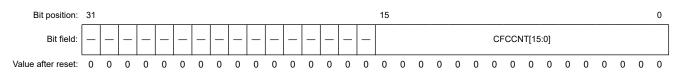

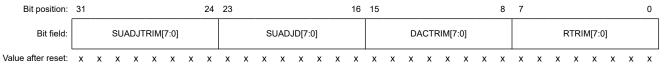

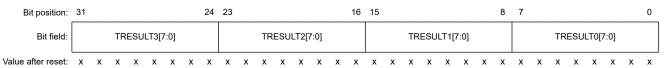

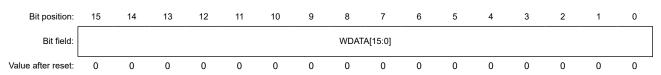

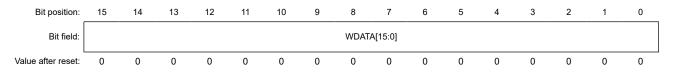

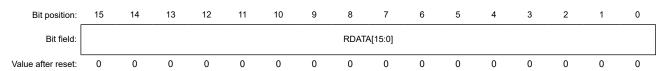

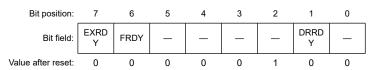

#### (2) Bit number

This number indicates the bit number. This bits are shown in order from bits 31 to 0 for 32-bit register, from bits 15 to 0 for 16-bit register, and from bits 7 to 0 for 8-bit register.

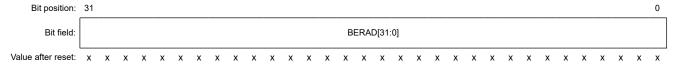

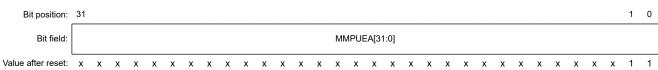

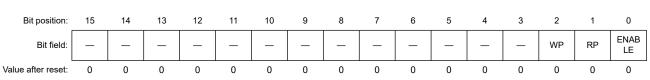

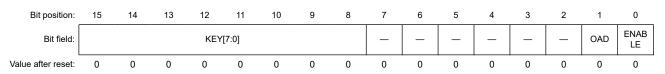

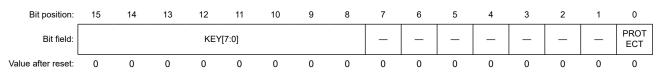

#### (3) Value after reset

This symbol or number indicate the value of each bit after a hard reset. The value is shown in binary unless specified otherwise.

- 0: Indicates that the value is 0 after a reset.

- 1: Indicates that the value is 1 after a reset.

- x: Indicates that the value is undefined after a reset.

#### (4) Symbol

Symbol indicates the short name of bit field. Reserved bit is expressed with a —.

#### (5) Function

Function indicates the full name of the bit field and enumerated values.

#### (6) R/W

The R/W column indicates access type whether the bit field is readable or writable.

R/W: The bit field is readable and writable.

- R: The bit field is readable only. Writing to this bit field has no effect.

- W: The bit field is writable only. The read value is the same as after a reset unless specified otherwise.

## 9. Abbreviations

Abbreviations used in this document are shown in the following table.

| Abbreviation | Description                                 |

|--------------|---------------------------------------------|

| AES          | Advanced Encryption Standard                |

| AHB          | Advanced High-performance Bus               |

| AHB-AP       | AHB Access Port                             |

| APB          | Advanced Peripheral Bus                     |

| ARC          | Alleged RC                                  |

| ATB          | Advanced Trace Bus                          |

| BCD          | Binary Coded Decimal                        |

| BSDL         | Boundary Scan Description Language          |

| DES          | Data Encryption Standard                    |

| DSA          | Digital Signature Algorithm                 |

| ETB          | Embedded Trace Buffer                       |

| ETM          | Embedded Trace Macrocell                    |

| FLL          | Frequency Locked Loop                       |

| FPU          | Floating Point Unit                         |

| НМІ          | Human Machine Interface                     |

| IrDA         | Infrared Data Association                   |

| LSB          | Least Significant Bit                       |

| MSB          | Most Significant Bit                        |

| NVIC         | Nested Vector Interrupt Controller          |

| PC           | Program Counter                             |

| PFS          | Port Function Select                        |

| PLL          | Phase Locked Loop                           |

| POR          | Power-on reset                              |

| PWM          | Pulse Width Modulation                      |

| RSA          | Rivest Shamir Adleman                       |

| SHA          | Secure Hash Algorithm                       |

| S/H          | Sample and Hold                             |

| SP           | Stack Pointer                               |

| SWD          | Serial Wire Debug                           |

| SW-DP        | Serial Wire-Debug Port                      |

| TRNG         | True Random Number Generator                |

| UART         | Universal Asynchronous Receiver/Transmitter |

| VCO          | Voltage Controlled Oscillator               |

## 10. Proprietary Notice

All text, graphics, photographs, trademarks, logos, artwork and computer code, collectively known as content, contained in this document is owned, controlled or licensed by or to Renesas, and is protected by trade dress, copyright, patent and trademark laws, and other intellectual property rights and unfair competition laws. Except as expressly provided herein, no part of this document or content may be copied, reproduced, republished, posted, publicly displayed, encoded, translated, transmitted or distributed in any other medium for publication or distribution or for any commercial enterprise, without prior written consent from Renesas.

Arm® and Cortex® are registered trademarks of Arm Limited.CoreSight™ is a trademark of Arm Limited.

CoreMark® is a registered trademark of the Embedded Microprocessor Benchmark Consortium.

SuperFlash® is a registered trademark of Silicon Storage Technology, Inc. in several countries including the United States and Japan.

Other brands and names mentioned in this document may be the trademarks or registered trademarks of their respective holders.

### 11. Feedback on the product

If you have any comments or suggestions about this product, go to Contact Us.

## Contents

| Fe | atures             |                                            | 36 |

|----|--------------------|--------------------------------------------|----|

| 1. | Overview.          |                                            | 37 |

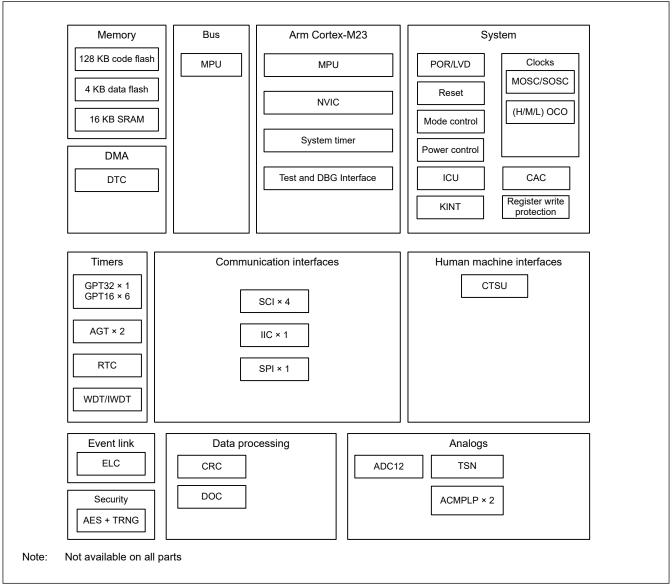

|    | 1.1 Func           | ction Outline                              | 37 |

|    | 1.2 Block          | k Diagram                                  | 42 |

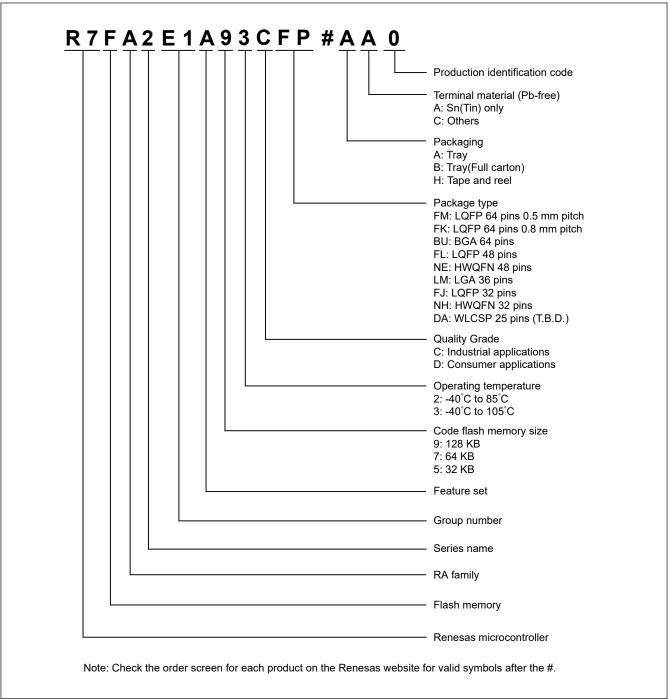

|    | 1.3 Part           | Numbering                                  | 42 |

|    | 1.4 Func           | tion Comparison                            | 46 |

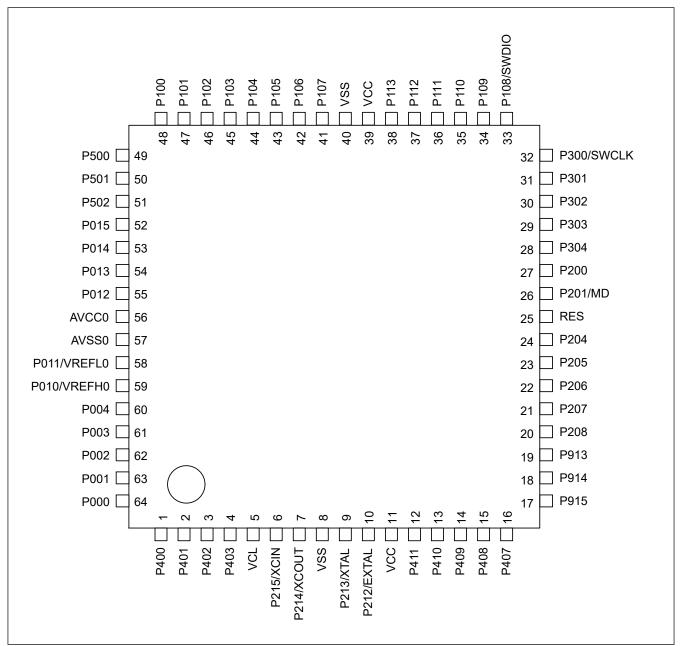

|    | 1.5 Pin F          | -unctions                                  | 48 |

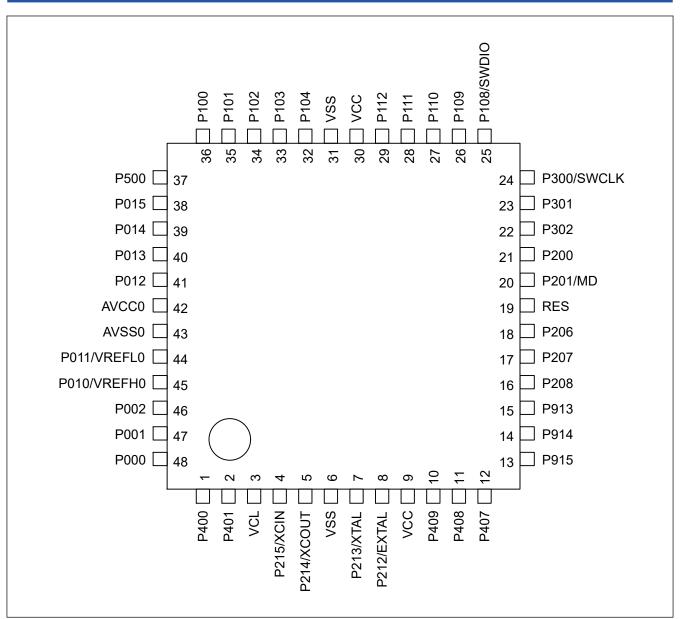

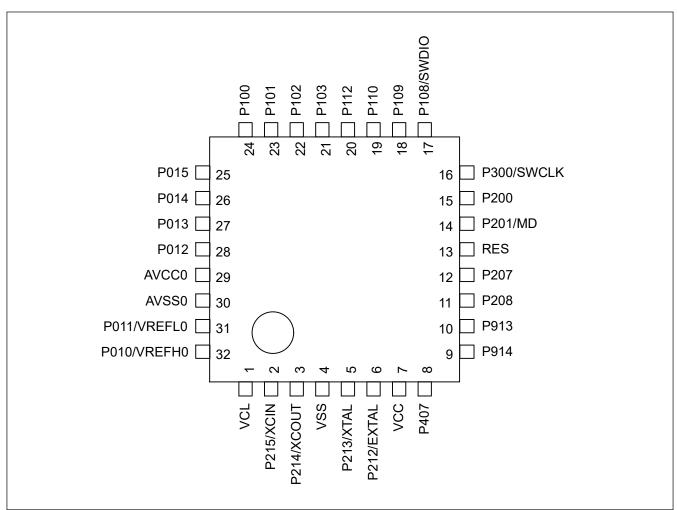

|    | 1.6 Pin A          | Assignments                                | 51 |

|    | 1.7 Pin L          | ists                                       | 57 |

| 2. | CPU                |                                            | 60 |

|    |                    | view                                       |    |

|    | 2.1.1              | CPU                                        | 60 |

|    | 2.1.2              | Debug                                      | 60 |

|    | 2.1.3              | Operating Frequency                        | 60 |

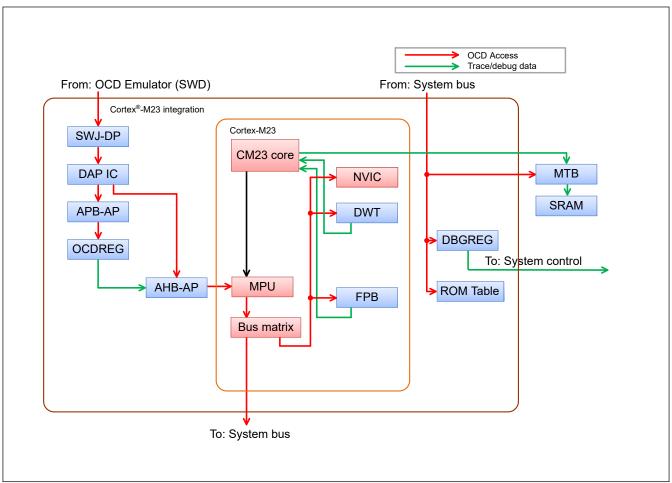

|    | 2.1.4              | Block Diagram                              | 60 |

|    | 2.2 Imple          | ementation Options                         | 61 |

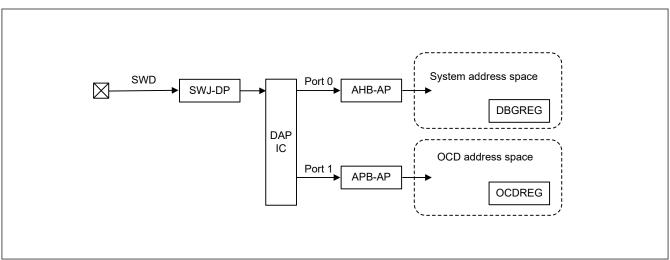

|    | 2.3 SWD            | ) Interface                                | 62 |

|    | 2.4 Debug Function |                                            | 62 |

|    | 2.4.1              | Debug Mode Definition                      | 62 |

|    | 2.4.2              | Debug Mode Effects                         | 62 |

|    | 2.5 Prog           | rammers Model                              | 63 |

|    | 2.5.1              | Address Spaces                             | 63 |

|    | 2.5.2              | Cortex-M23 Peripheral Address Map          | 64 |

|    | 2.5.3              | External Debug Address Map                 | 64 |

|    | 2.5.4              | CoreSight ROM Table                        | 64 |

|    | 2.5.5              | DBGREG Module                              | 65 |

|    | 2.5.6              | OCDREG Module                              | 67 |

|    | 2.6 SysT           | ick Timer                                  | 69 |

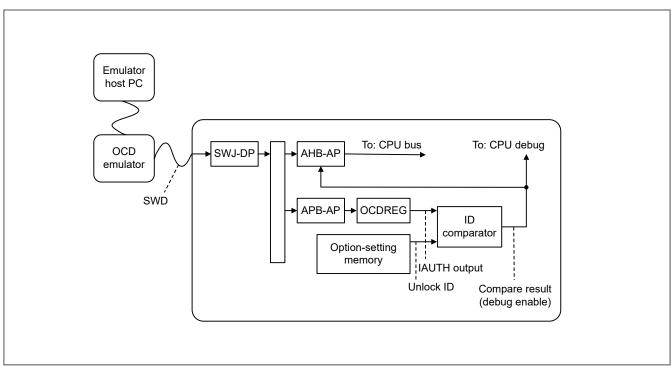

|    | 2.7 OCD            | Emulator Connection                        | 69 |

|    | 2.7.1              | Unlock ID Code                             | 70 |

|    | 2.7.2              | DBGEN                                      | 70 |

|    | 2.7.3              | Restrictions on Connecting an OCD emulator | 70 |

|    | 2.8 Refe           | rences                                     | 72 |

|    | 2.9 Usag           | ge Notes                                   | 72 |

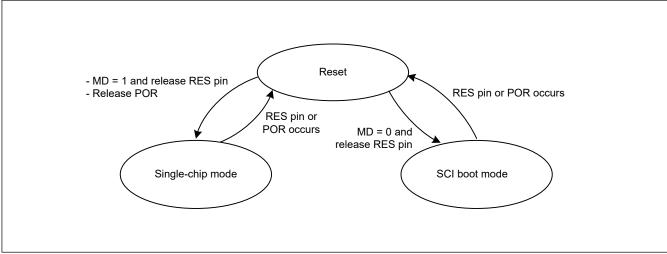

| 3. | Operating          | Modes                                      | 73 |

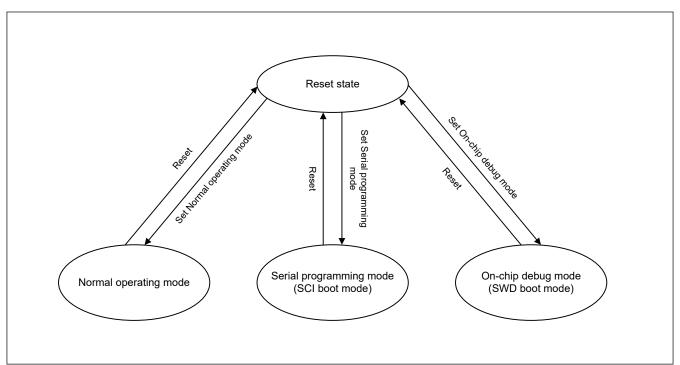

|    | 3.1 Oper           | rating Mode Types and Selection            | 73 |

|    | 3.2 Detai          | ils of Operating Modes                     | 73 |

|    | 3.2.1      | Single-Chip Mode                                                                | 73     |

|----|------------|---------------------------------------------------------------------------------|--------|

|    | 3.2.2      | SCI Boot Mode                                                                   | 73     |

|    | 3.3 Opera  | ating Modes Transitions                                                         | 73     |

|    | 3.3.1      | Operating Mode Transitions as Determined by the Mode-Setting Pin                | 73     |

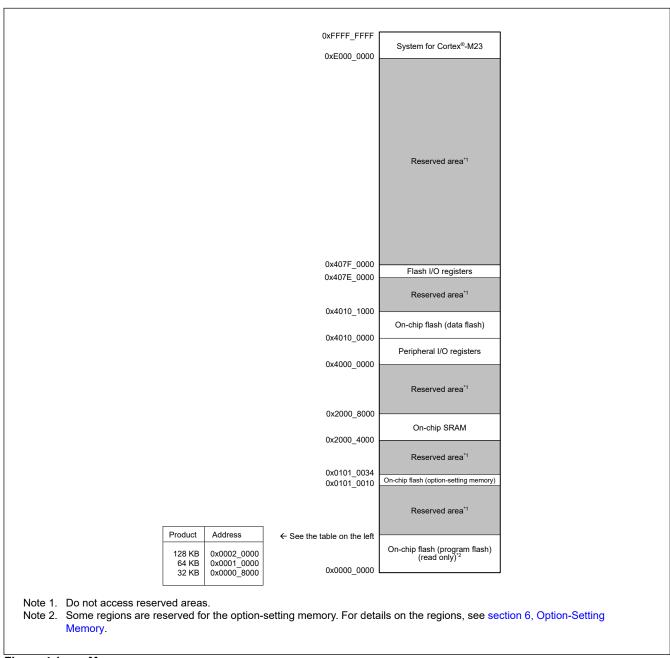

| 4. | Address S  | pace                                                                            | 74     |

|    | 4.1 Addre  | ess Space                                                                       | 74     |

| 5. | Resets     |                                                                                 | 75     |

|    |            | view                                                                            |        |

|    | 5.2 Regis  | ster Descriptions                                                               | 80     |

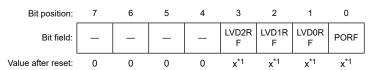

|    | 5.2.1      | RSTSR0 : Reset Status Register 0                                                | 80     |

|    | 5.2.2      | RSTSR1 : Reset Status Register 1                                                | 81     |

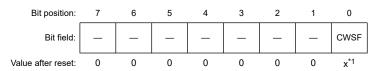

|    | 5.2.3      | RSTSR2 : Reset Status Register 2                                                | 83     |

|    | 5.3 Opera  | ation                                                                           | 83     |

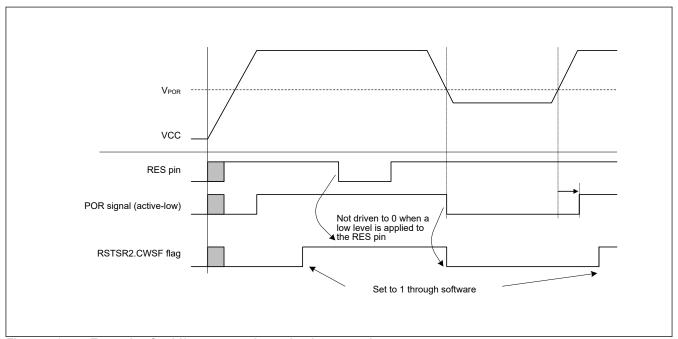

|    | 5.3.1      | RES Pin Reset                                                                   | 83     |

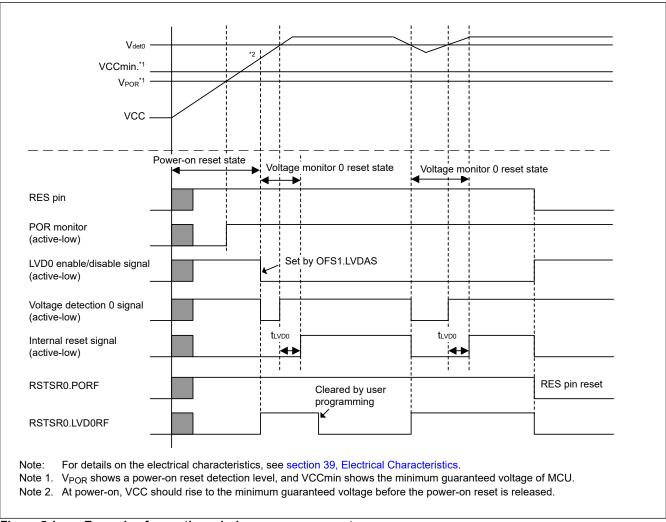

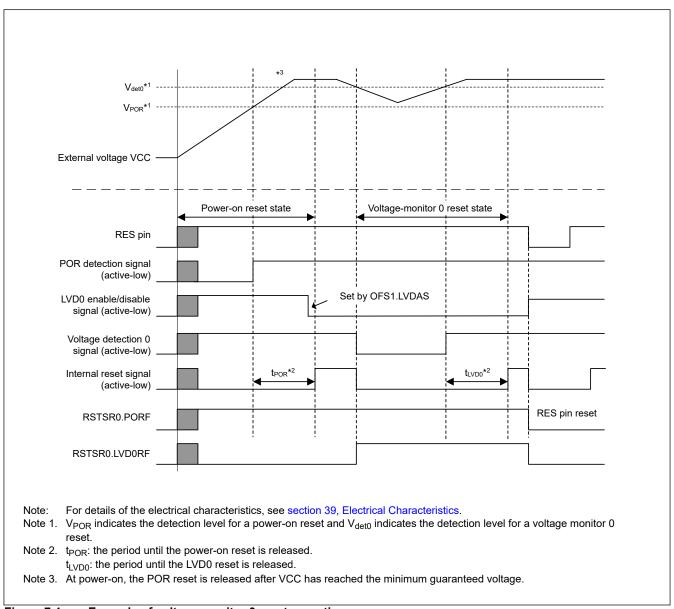

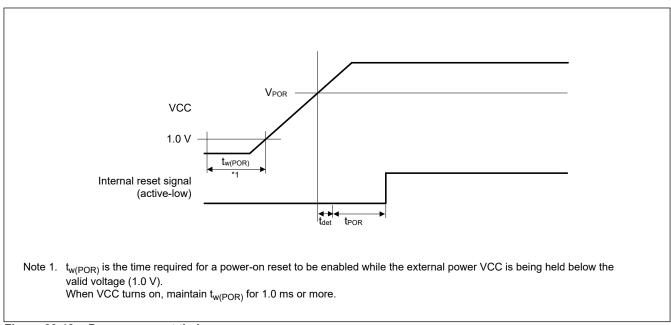

|    | 5.3.2      | Power-On Reset                                                                  | 84     |

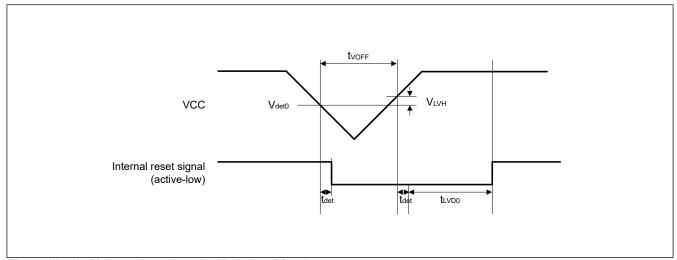

|    | 5.3.3      | Voltage Monitor Reset                                                           | 84     |

|    | 5.3.4      | Independent Watchdog Timer Reset                                                | 86     |

|    | 5.3.5      | Watchdog Timer Reset                                                            | 86     |

|    | 5.3.6      | Software Reset                                                                  | 86     |

|    | 5.3.7      | Determination of Cold/Warm Start                                                | 86     |

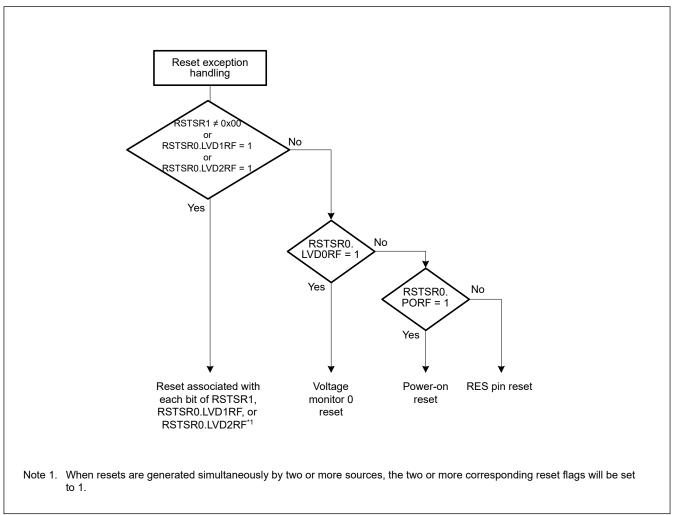

|    | 5.3.8      | Determination of Reset Generation Source                                        | 87     |

|    | 5.4 Usag   | e Notes                                                                         | 87     |

|    | 5.4.1      | Note on RES pin reset                                                           | 87     |

| 6. | Option-Se  | tting Memory                                                                    | 88     |

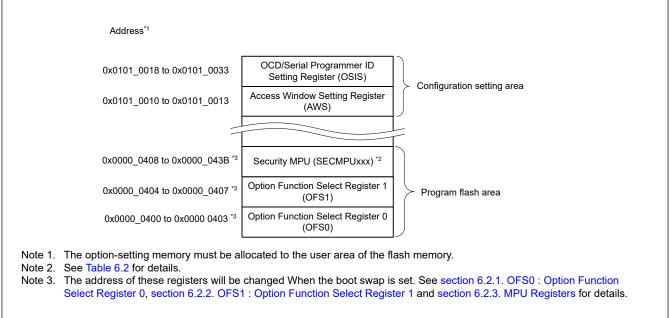

|    | 6.1 Over   | view                                                                            | 88     |

|    | 6.2 Regis  | ster Descriptions                                                               | 88     |

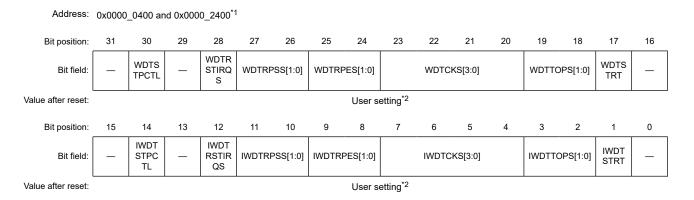

|    | 6.2.1      | OFS0 : Option Function Select Register 0                                        | 88     |

|    | 6.2.2      | OFS1 : Option Function Select Register 1                                        | 92     |

|    | 6.2.3      | MPU Registers                                                                   | 93     |

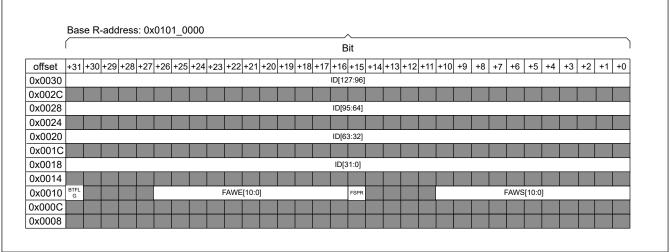

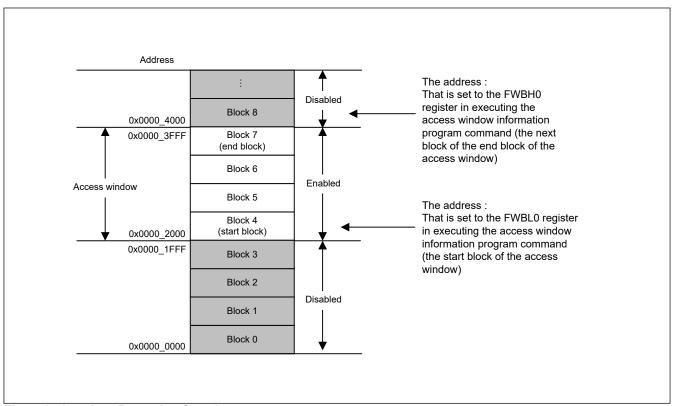

|    | 6.2.4      | AWS : Access Window Setting Register                                            | 94     |

|    | 6.2.5      | OSIS : OCD/Serial Programmer ID Setting Register                                | 95     |

|    | 6.3 Settir | ng Option-Setting Memory                                                        | 96     |

|    | 6.3.1      | Allocation of Data in Option-Setting Memory                                     | 96     |

|    | 6.3.2      | Setting Data for Programming Option-Setting Memory                              | 96     |

|    | 6.4 Usag   | e Notes                                                                         | 97     |

|    | 6.4.1      | Data for Programming Reserved Areas and Reserved Bits in the Option-Setting Men | nory97 |

|    | 6.4.2      | Note on FSPR Bit                                                                | 97     |

| 7. | Low Voltag | ge Detection (LVD)                                                              | 98     |

|    | 7.1 Over   | view                                                                            | 98     |

|    | 7.2 Regis   | ter Descriptions                                                | 100 |

|----|-------------|-----------------------------------------------------------------|-----|

|    | 7.2.1       | LVCMPCR : Voltage Monitor Circuit Control Register              | 100 |

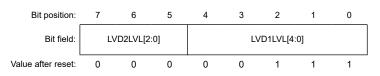

|    | 7.2.2       | LVDLVLR : Voltage Detection Level Select Register               | 101 |

|    | 7.2.3       | LVD1CR0 : Voltage Monitor 1 Circuit Control Register 0          | 101 |

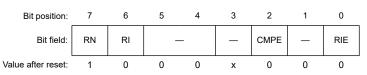

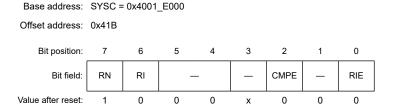

|    | 7.2.4       | LVD2CR0 : Voltage Monitor 2 Circuit Control Register 0          | 102 |

|    | 7.2.5       | LVD1CR1 : Voltage Monitor 1 Circuit Control Register            | 103 |

|    | 7.2.6       | LVD1SR : Voltage Monitor 1 Circuit Status Register              | 103 |

|    | 7.2.7       | LVD2CR1 : Voltage Monitor 2 Circuit Control Register 1          | 104 |

|    | 7.2.8       | LVD2SR : Voltage Monitor 2 Circuit Status Register              | 104 |

|    | 7.3 VCC I   | Input Voltage Monitor                                           | 105 |

|    | 7.3.1       | Monitoring Vdet0                                                | 105 |

|    | 7.3.2       | Monitoring Vdet1                                                | 105 |

|    | 7.3.3       | Monitoring Vdet2                                                | 105 |

|    | 7.4 Reset   | t from Voltage Monitor 0                                        | 106 |

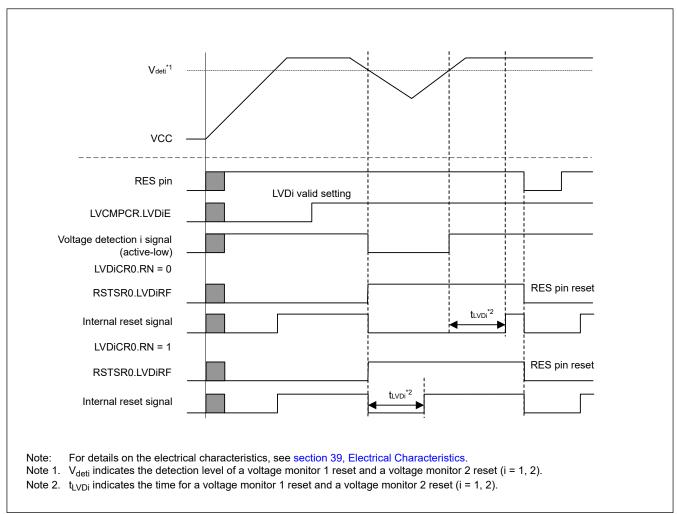

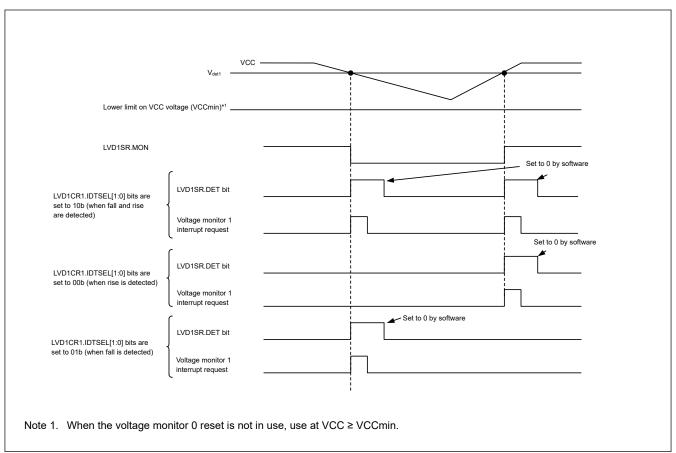

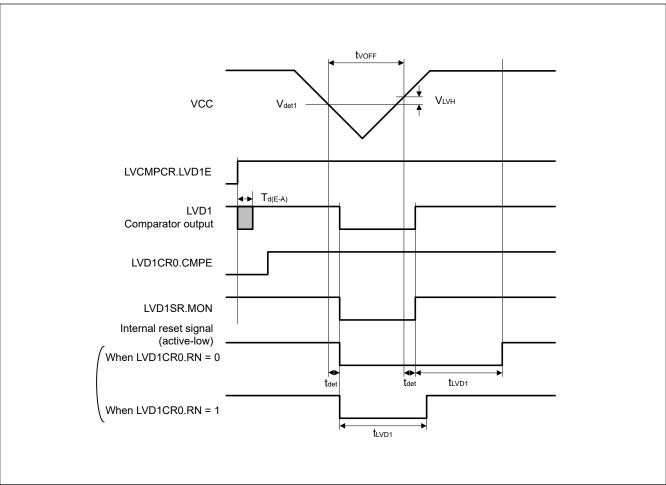

|    | 7.5 Interru | upt and Reset from Voltage Monitor 1                            | 106 |

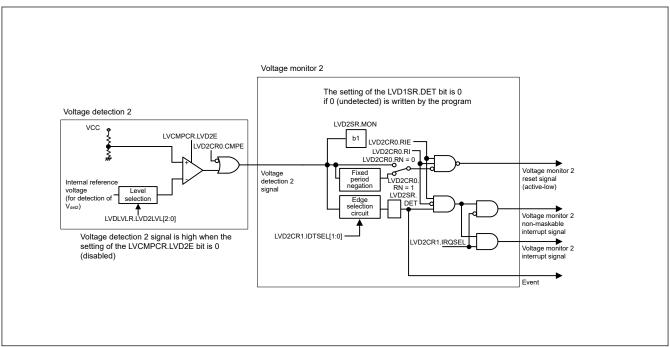

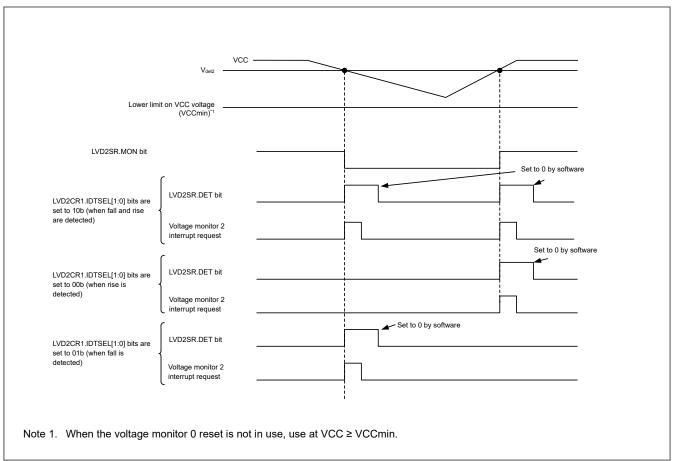

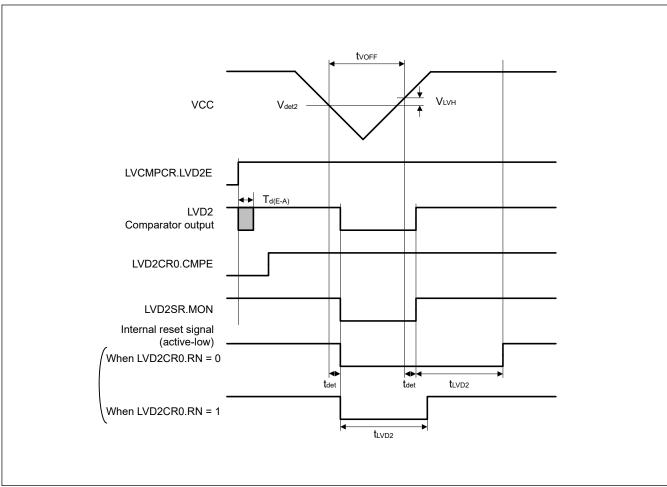

|    | 7.6 Interru | upt and Reset from Voltage Monitor 2                            | 108 |

|    | 7.7 Event   | Link Controller (ELC) Output                                    | 110 |

|    | 7.7.1       | Interrupt Handling and Event Linking                            | 110 |

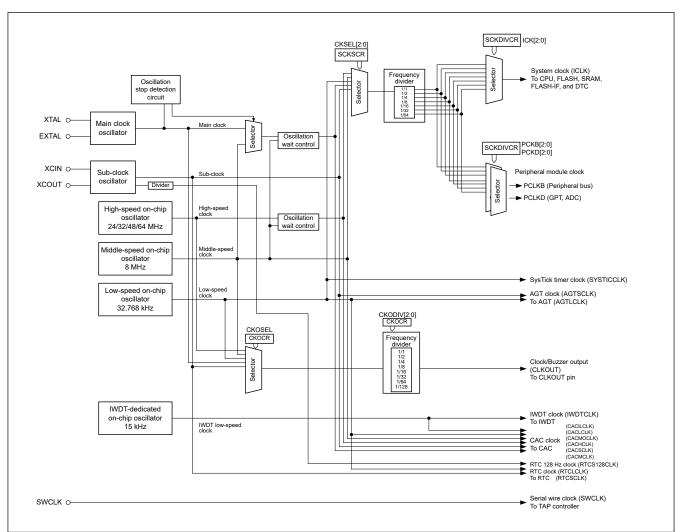

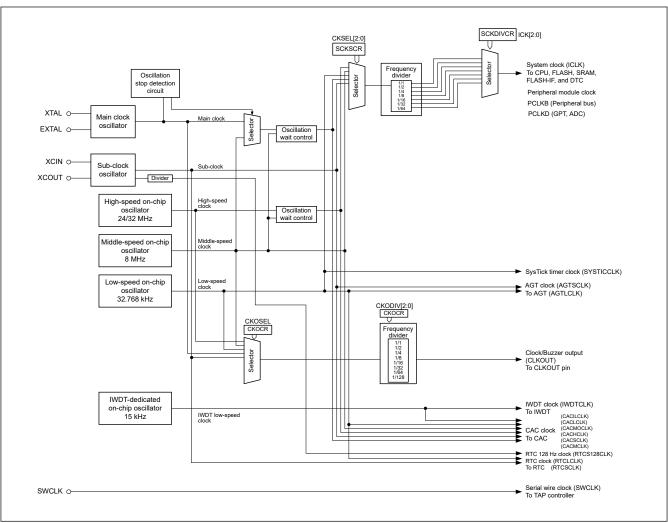

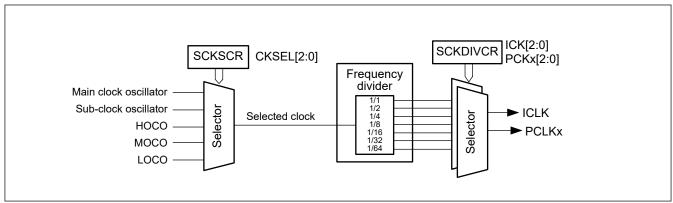

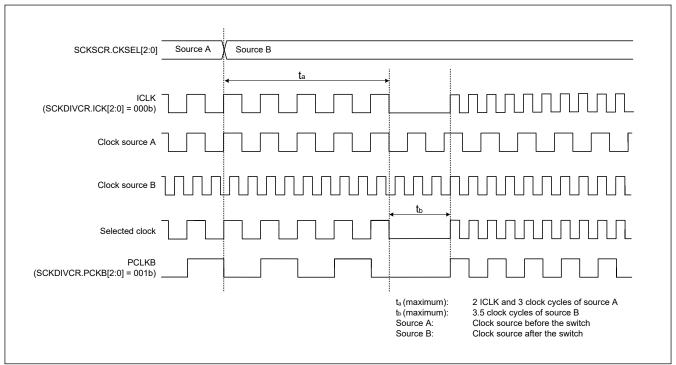

| 8. | Clock Gen   | eration Circuit                                                 | 112 |

|    | 8.1 Overv   | /iew                                                            | 112 |

|    | 8.2 Regis   | ter Descriptions                                                | 115 |

|    | 8.2.1       | SCKDIVCR : System Clock Division Control Register               | 115 |

|    | 8.2.2       | SCKSCR : System Clock Source Control Register                   | 116 |

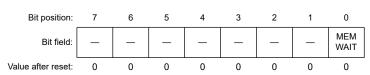

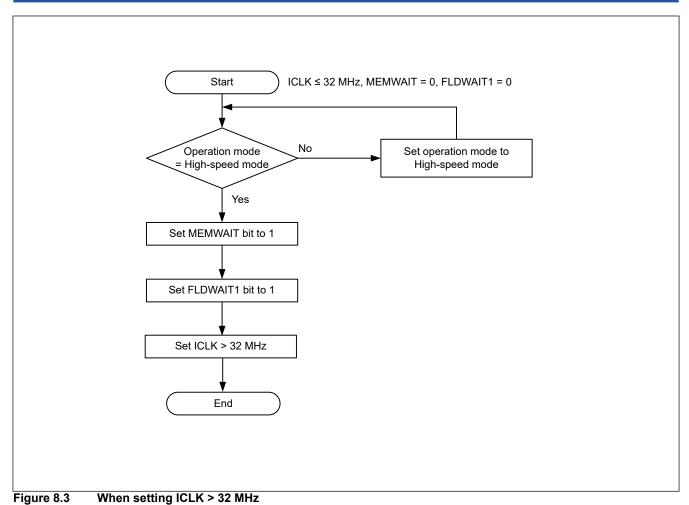

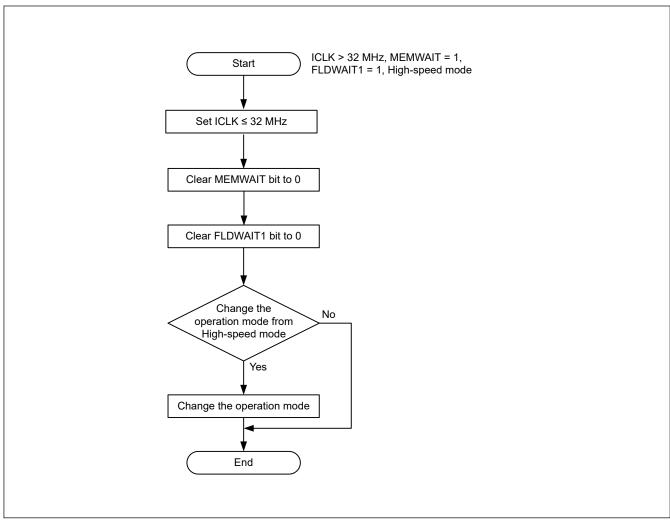

|    | 8.2.3       | MEMWAIT : Memory Wait Cycle Control Register for Code Flash     | 116 |

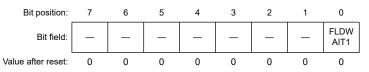

|    | 8.2.4       | FLDWAITR : Memory Wait Cycle Control Register for Data Flash    | 117 |

|    | 8.2.5       | MOSCCR : Main Clock Oscillator Control Register                 | 120 |

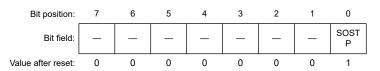

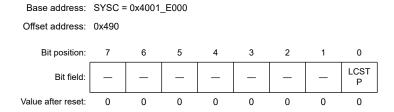

|    | 8.2.6       | SOSCCR : Sub-Clock Oscillator Control Register                  | 121 |

|    | 8.2.7       | LOCOCR : Low-Speed On-Chip Oscillator Control Register          | 122 |

|    | 8.2.8       | HOCOCR : High-Speed On-Chip Oscillator Control Register         | 122 |

|    | 8.2.9       | MOCOCR : Middle-Speed On-Chip Oscillator Control Register       | 123 |

|    | 8.2.10      | OSCSF : Oscillation Stabilization Flag Register                 | 124 |

|    | 8.2.11      | OSTDCR : Oscillation Stop Detection Control Register            | 125 |

|    | 8.2.12      | OSTDSR : Oscillation Stop Detection Status Register             | 126 |

|    | 8.2.13      | MOSCWTCR : Main Clock Oscillator Wait Control Register          | 126 |

|    | 8.2.14      | HOCOWTCR : High-Speed On-Chip Oscillator Wait Control Register  | 127 |

|    | 8.2.15      | MOMCR : Main Clock Oscillator Mode Oscillation Control Register | 128 |

|    | 8.2.16      | SOMCR : Sub-Clock Oscillator Mode Control Register              | 128 |

|    | 8.2.17      | SOMRG : Sub-Clock Oscillator Margin Check Register              | 129 |

|    | 8.2.18      | CKOCR : Clock Out Control Register                              | 129 |

|    | 8.2.19      | LOCOUTCR: LOCO User Trimming Control Register                   | 130 |

|    | 8.2.20     | MOCOUTCR: MOCO User Trimming Control Register            | 131 |

|----|------------|----------------------------------------------------------|-----|

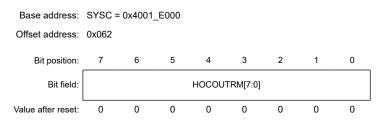

|    | 8.2.21     | HOCOUTCR : HOCO User Trimming Control Register           | 131 |

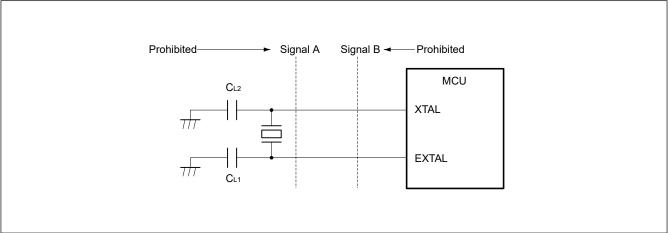

|    | 8.3 Main   | Clock Oscillator                                         | 131 |

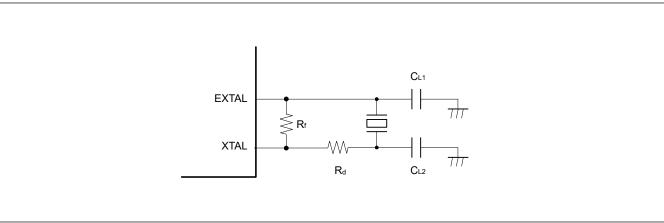

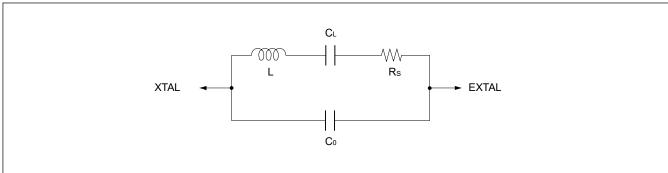

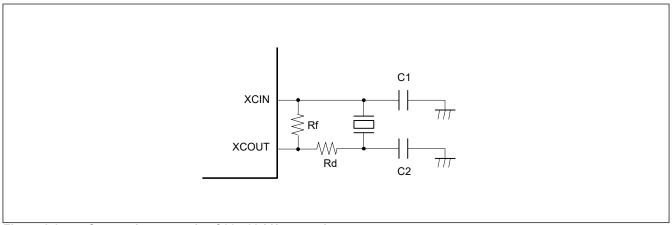

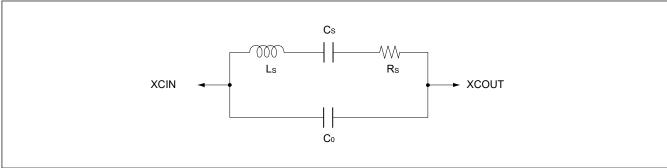

|    | 8.3.1      | Connecting a Crystal Resonator                           | 132 |

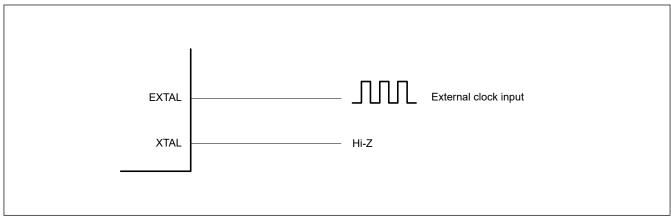

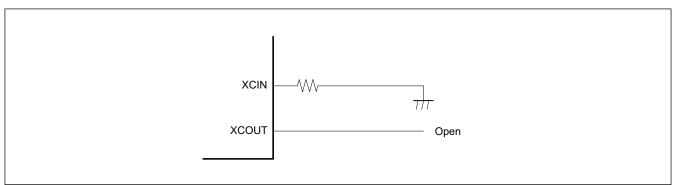

|    | 8.3.2      | External Clock Input                                     | 132 |

|    | 8.3.3      | Notes on External Clock Input                            | 133 |

|    | 8.4 Sub-0  | Clock Oscillator                                         | 133 |

|    | 8.4.1      | Connecting a 32.768-kHz Crystal Resonator                | 133 |

|    | 8.4.2      | Pin Handling When the Sub-Clock Oscillator Is Not Used   | 134 |

|    | 8.5 Oscill | ation Stop Detection Function                            | 134 |

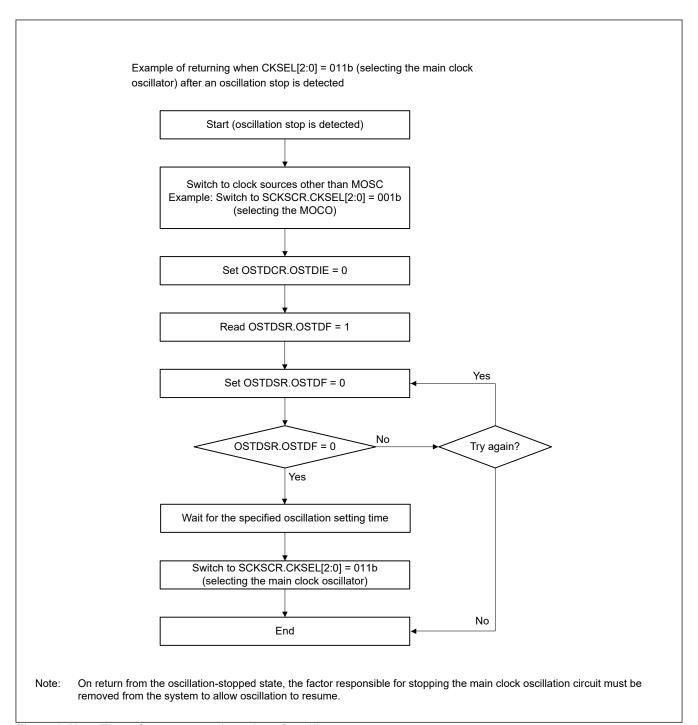

|    | 8.5.1      | Oscillation Stop Detection and Operation after Detection | 134 |

|    | 8.5.2      | Oscillation Stop Detection Interrupts                    | 136 |

|    | 8.6 Intern | al Clock                                                 | 136 |

|    | 8.6.1      | System Clock (ICLK)                                      | 136 |

|    | 8.6.2      | Peripheral Module Clock (PCLKB, PCLKD)                   | 137 |

|    | 8.6.3      | CAC Clock (CACCLK)                                       | 137 |

|    | 8.6.4      | RTC-Dedicated Clock (RTCSCLK, RTCS128CLK, RTCLCLK)       | 138 |

|    | 8.6.5      | IWDT-Dedicated Clock (IWDTCLK)                           | 138 |

|    | 8.6.6      | AGT-Dedicated Clock (AGTSCLK, AGTLCLK)                   | 138 |

|    | 8.6.7      | SysTick Timer-Dedicated Clock (SYSTICCLK)                | 138 |

|    | 8.6.8      | External Pin Output Clock (CLKOUT)                       | 138 |

|    | 8.7 Usage  | e Notes                                                  | 138 |

|    | 8.7.1      | Notes on Clock Generation Circuit                        | 138 |

|    | 8.7.2      | Notes on Resonator                                       | 138 |

|    | 8.7.3      | Notes on Board Design                                    | 139 |

|    | 8.7.4      | Notes on Resonator Connect Pin                           | 139 |

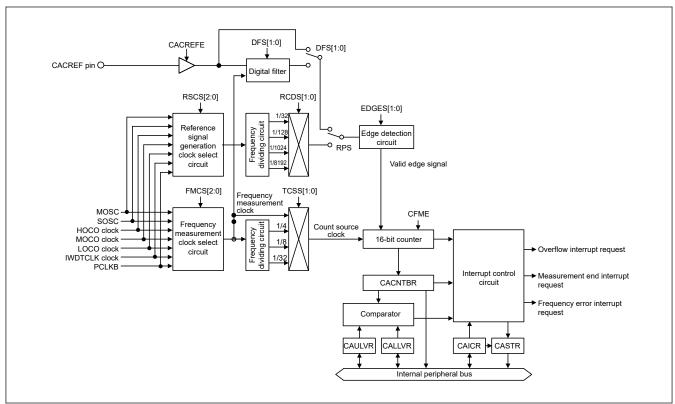

| 9. | Clock Fred | quency Accuracy Measurement Circuit (CAC)                | 140 |

|    |            | . , , , , , , , , , , , , , , , , , , ,                  |     |

|    | 9.2 Regis  | ster Descriptions                                        | 141 |

|    | 9.2.1      | CACR0 : CAC Control Register 0                           | 141 |

|    | 9.2.2      | CACR1 : CAC Control Register 1                           | 142 |

|    | 9.2.3      | CACR2 : CAC Control Register 2                           | 142 |

|    | 9.2.4      | CAICR : CAC Interrupt Control Register                   | 143 |

|    | 9.2.5      | CASTR : CAC Status Register                              | 144 |

|    | 9.2.6      | CAULVR : CAC Upper-Limit Value Setting Register          | 145 |

|    | 9.2.7      | CALLVR : CAC Lower-Limit Value Setting Register          | 145 |

|    | 9.2.8      | CACNTBR : CAC Counter Buffer Register                    | 146 |

|    | 9.3 Opera  | ation                                                    | 146 |

|    | 9.3.1      | Measuring Clock Frequency                                | 146 |

|    | 9.3.2      | Digital Filtering of Signals on CACREF Pin               | 147 |

|    |            |                                                          |     |

|           | 9.4  | Interrup | t Requests                                               | 147 |

|-----------|------|----------|----------------------------------------------------------|-----|

| 9.5 Usage |      | Usage I  | Notes                                                    | 148 |

|           | 9.   | 5.1      | Settings for the Module-Stop Function                    | 148 |

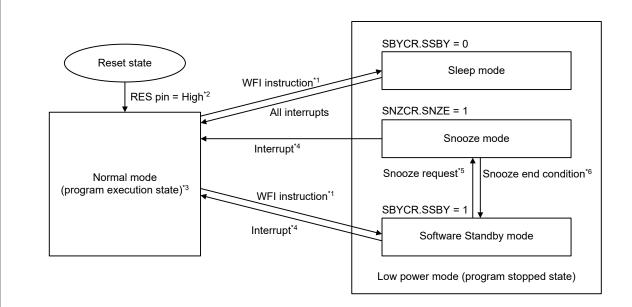

| 10.       | Low  | Power N  | Modes                                                    | 149 |

|           | 10.1 | Overvie  | •W                                                       | 149 |

|           | 10.2 | Registe  | r Descriptions                                           | 152 |

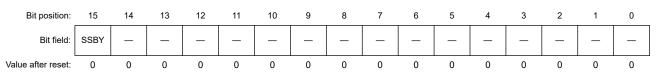

|           | 10   | ).2.1    | SBYCR : Standby Control Register                         | 152 |

|           | 10   | ).2.2    | MSTPCRA : Module Stop Control Register A                 | 153 |

|           | 10   | ).2.3    | MSTPCRB : Module Stop Control Register B                 | 153 |

|           | 10   | ).2.4    | MSTPCRC : Module Stop Control Register C                 | 154 |

|           | 10   | ).2.5    | MSTPCRD : Module Stop Control Register D                 | 155 |

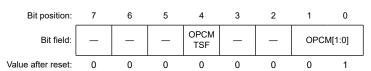

|           | 10   | ).2.6    | OPCCR : Operating Power Control Register                 | 156 |

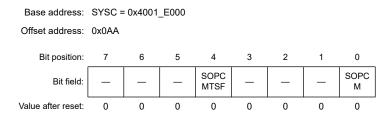

|           | 10   | ).2.7    | SOPCCR : Sub Operating Power Control Register            | 157 |

|           | 10   | ).2.8    | SNZCR : Snooze Control Register                          | 158 |

|           | 10   | ).2.9    | SNZEDCR0 : Snooze End Control Register 0                 | 159 |

|           | 10   | ).2.10   | SNZREQCR0 : Snooze Request Control Register 0            | 160 |

|           | 10   | ).2.11   | PSMCR : Power Save Memory Control Register               | 161 |

|           | 10   | ).2.12   | SYOCDCR : System Control OCD Control Register            | 162 |

|           | 10   | ).2.13   | LSMRWDIS : Low Speed Module R/W Disable Control Register | 162 |

|           | 10   | ).2.14   | LPOPT : Lower Power Operation Control Register           | 163 |

|           | 10.3 | Reducir  | ng Power Consumption by Switching Clock Signals          | 164 |

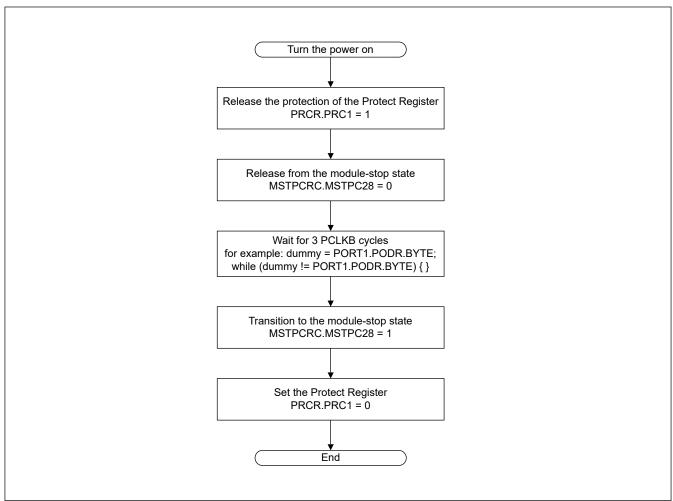

|           | 10.4 | Module-  | -Stop Function                                           | 164 |

|           | 10.5 | Function | n for Lower Operating Power Consumption                  | 164 |

|           | 10   | ).5.1    | Setting Operating Power Control Mode                     | 165 |

|           | 10   | ).5.2    | Operating Range                                          | 166 |

|           | 10.6 | Sleep M  | Mode                                                     | 168 |

|           | 10   | ).6.1    | Transitioning to Sleep Mode                              | 168 |

|           | 10   | 0.6.2    | Canceling Sleep Mode                                     | 168 |

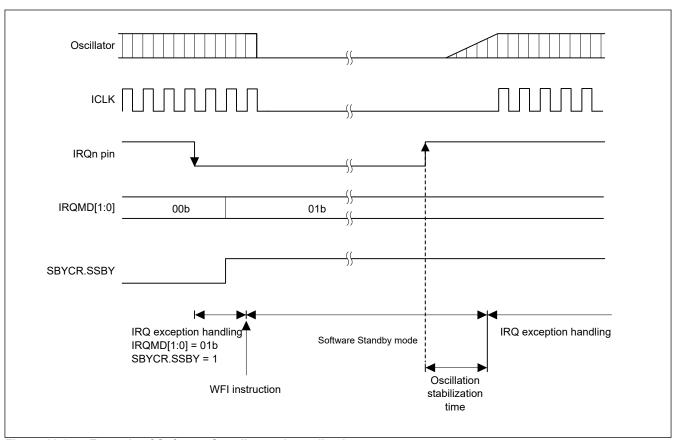

|           | 10.7 | Softwar  | e Standby Mode                                           | 169 |

|           | 10   | ).7.1    | Transition to Software Standby Mode                      | 169 |

|           | 10   | ).7.2    | Canceling Software Standby Mode                          | 169 |

|           | 10   | ).7.3    | Example of Software Standby Mode Application             | 170 |

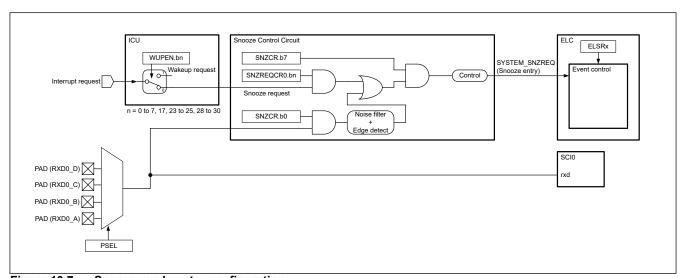

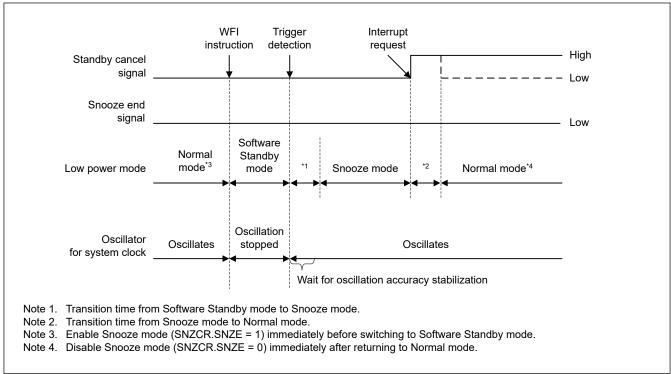

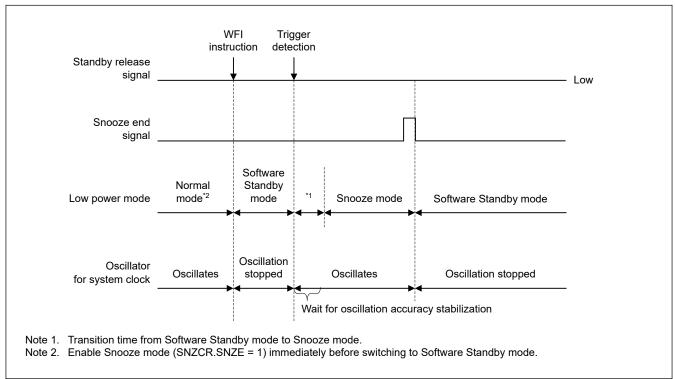

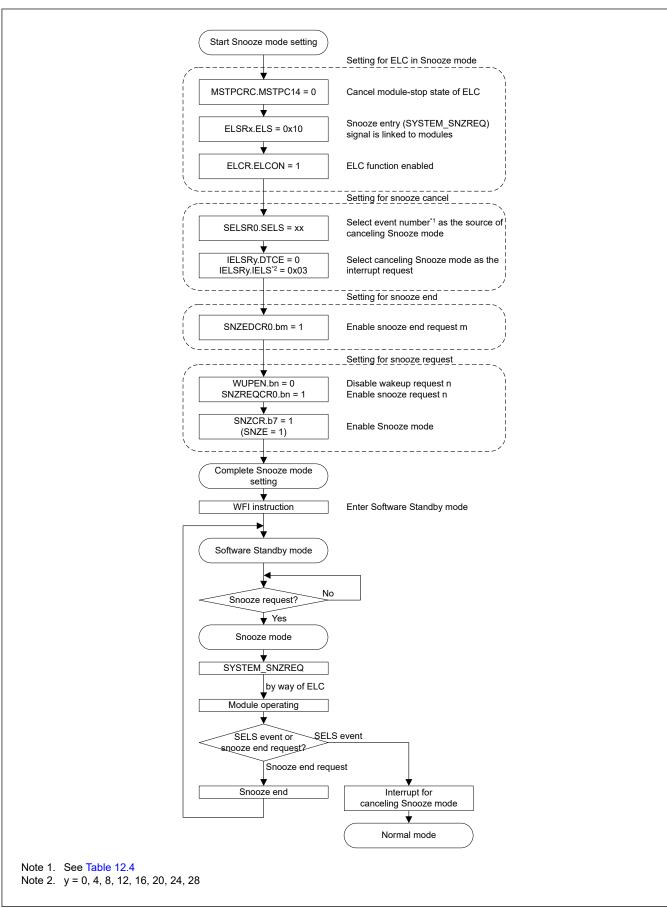

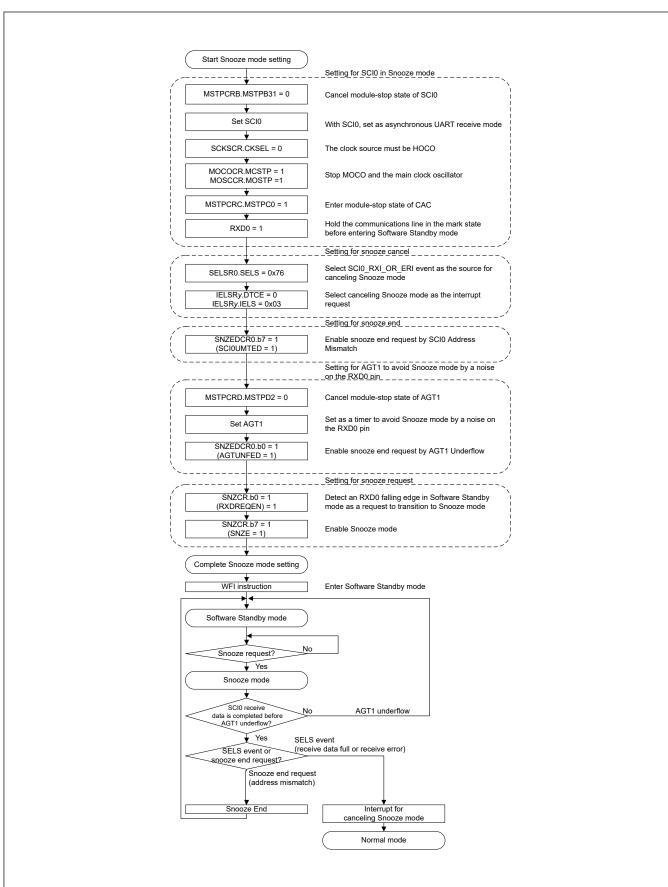

|           | 10.8 | Snooze   | Mode                                                     | 171 |

|           | 10   | ).8.1    | Transition to Snooze Mode                                | 171 |

|           | 10   | ).8.2    | Canceling Snooze Mode                                    | 172 |

|           | 10   | 0.8.3    | Returning from Snooze Mode to Software Standby Mode      | 173 |

|           | 10   | ).8.4    | Snooze Operation Example                                 | 174 |

|           | 10.9 | Usage I  | Notes                                                    | 178 |

|           | 10   | ).9.1    | Register Access                                          | 178 |

|           | 10   | ).9.2    | I/O Port pin states                                      | 179 |

|     | 10.9.3       | Module-Stop State of DTC                                              | 179 |

|-----|--------------|-----------------------------------------------------------------------|-----|

|     | 10.9.4       | Internal Interrupt Sources                                            | 179 |

|     | 10.9.5       | Transitioning to Low Power Modes                                      | 179 |

|     | 10.9.6       | Timing of WFI Instruction                                             | 179 |

|     | 10.9.7       | Writing to the WDT/IWDT Registers by DTC in Sleep Mode or Snooze Mode | 179 |

|     | 10.9.8       | Oscillators in Snooze Mode                                            | 179 |

|     | 10.9.9       | Snooze Mode Entry by RXD0 Falling Edge                                | 179 |

|     | 10.9.10      | Using UART of SCI0 in Snooze Mode                                     | 180 |

|     | 10.9.11      | Conditions of A/D Conversion Start in Snooze Mode                     | 180 |

|     | 10.9.12      | Conditions of CTSU in Snooze Mode                                     | 180 |

|     | 10.9.13      | ELC Events in Snooze Mode                                             | 180 |

|     | 10.9.14      | Module-Stop Function for ADC120                                       | 180 |

|     | 10.9.15      | Module-Stop Function for an Unused Circuit                            | 180 |

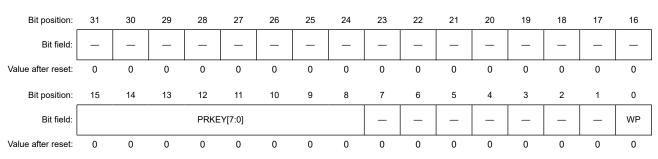

| 11. | Register Wi  | rite Protection                                                       | 182 |

|     | 11.1 Overvi  | ew                                                                    | 182 |

|     | 11.2 Regist  | er Descriptions                                                       | 182 |

|     | 11.2.1       | PRCR : Protect Register                                               | 182 |

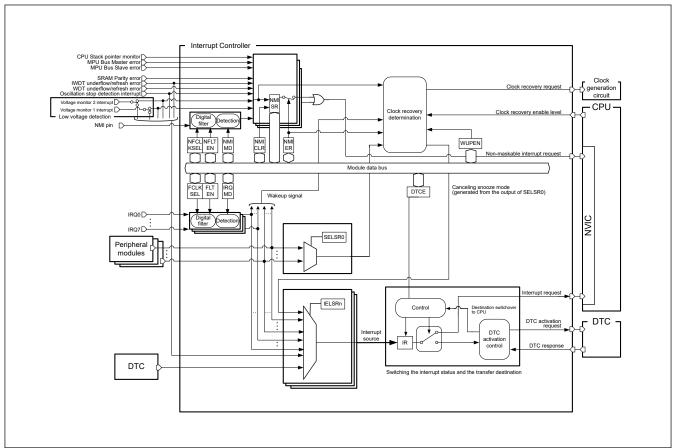

| 12  | Interrunt Co | ontroller Unit (ICU)                                                  | 183 |

| 12. | -            | ew                                                                    |     |

|     |              | er Descriptions                                                       |     |

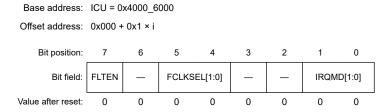

|     | 12.2.1       | IRQCRi : IRQ Control Register i (i = 0 to 7)                          |     |

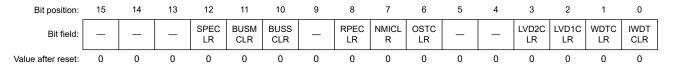

|     | 12.2.2       | NMISR : Non-Maskable Interrupt Status Register                        |     |

|     | 12.2.3       | NMIER : Non-Maskable Interrupt Enable Register                        |     |

|     | 12.2.4       | NMICLR : Non-Maskable Interrupt Status Clear Register                 |     |

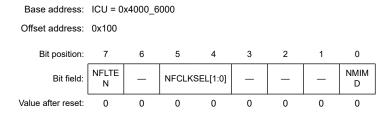

|     | 12.2.5       | NMICR : NMI Pin Interrupt Control Register                            |     |

|     | 12.2.6       | IELSRn : ICU Event Link Setting Register n (n = 0 to 31)              |     |

|     | 12.2.7       | SELSR0 : SYS Event Link Setting Register                              |     |

|     | 12.2.8       | WUPEN : Wake Up Interrupt Enable Register                             | 193 |

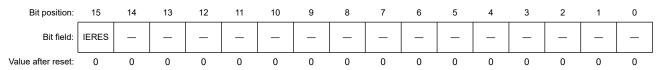

|     | 12.2.9       | IELEN : ICU event Enable Register                                     | 195 |

|     | 12.3 Vector  | Table                                                                 | 196 |

|     | 12.3.1       | Interrupt Vector Table                                                | 196 |

|     | 12.3.2       | Event Number                                                          | 197 |

|     | 12.3.3       | ICU and DTC Event Number                                              | 201 |

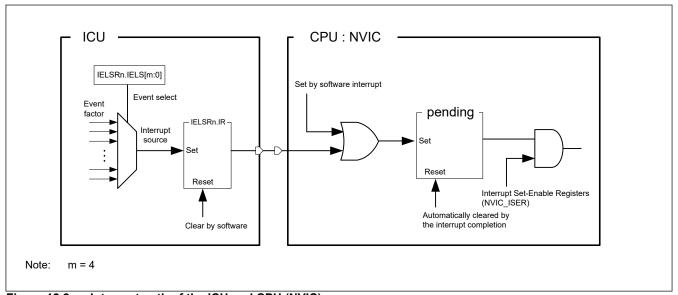

|     | 12.4 Interru | pt Operation                                                          | 206 |

|     | 12.4.1       | Detecting Interrupts                                                  | 206 |

|     | 12.5 Interru | pt setting procedure                                                  | 206 |

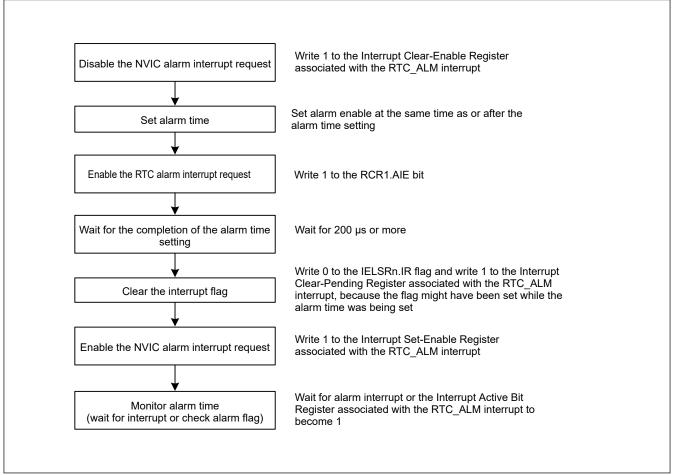

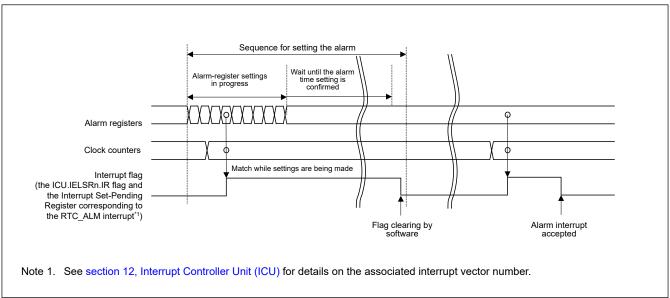

|     | 12.5.1       | Enabling Interrupt Requests                                           | 206 |

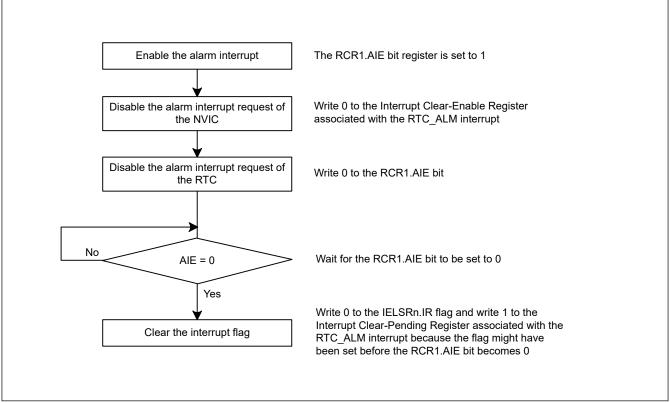

|     | 12.5.2       | Disabling Interrupt Requests                                          | 207 |

|     | 12.5.3       | Polling for interrupts                                                | 207 |

|     |              |                                                                       |     |

|     | •    | 12.5.4     | Selecting Interrupt Request Destinations                | 207 |

|-----|------|------------|---------------------------------------------------------|-----|

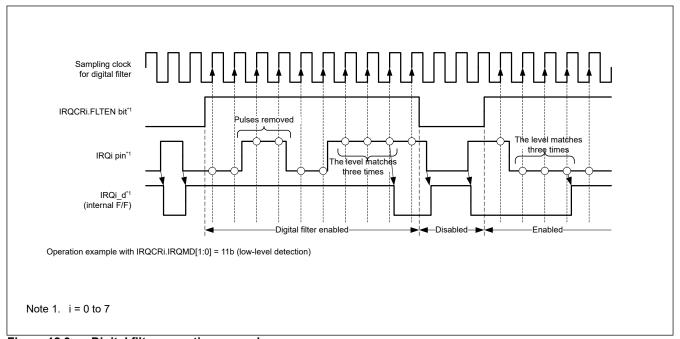

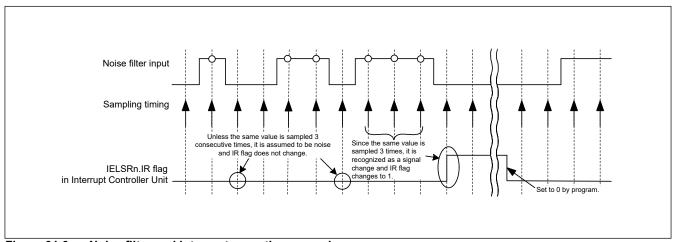

|     |      | 12.5.5     | Digital Filter                                          | 208 |

|     |      | 12.5.6     | External Pin Interrupts                                 | 208 |

|     | 12.6 | Non-Ma     | askable Interrupt Operation                             | 209 |

|     | 12.7 | ' Return   | from Low Power Modes                                    | 209 |

|     |      | 12.7.1     | Return from Sleep Mode                                  | 209 |

|     |      | 12.7.2     | Return from Software Standby Mode                       | 210 |

|     | •    | 12.7.3     | Return from Snooze Mode                                 | 210 |

|     | 12.8 | B Using th | he WFI Instruction with Non-Maskable Interrupts         | 210 |

|     | 12.9 | Referer    | nce                                                     | 210 |

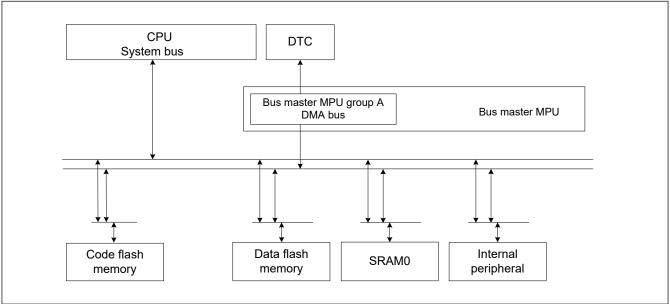

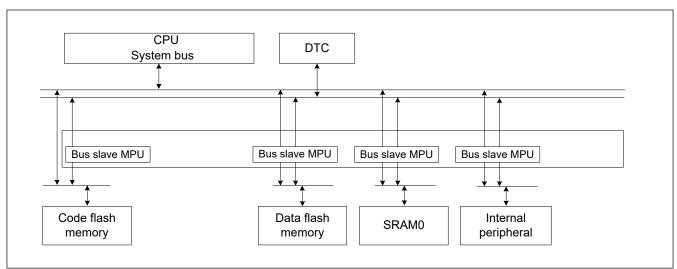

| 13. | Bu   | ses        |                                                         | 211 |

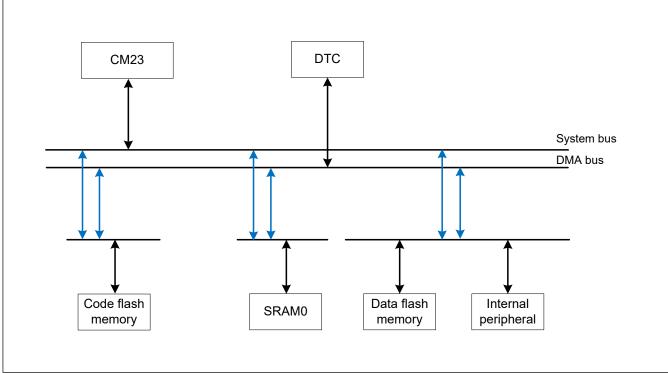

|     | 13.1 | Overvie    | ew                                                      | 211 |

|     | 13.2 | 2 Descrip  | otion of Buses                                          | 212 |

|     |      | 13.2.1     | Main Buses                                              | 212 |

|     |      | 13.2.2     | Slave Interface                                         | 212 |

|     |      | 13.2.3     | Parallel Operations                                     | 212 |

|     |      | 13.2.4     | Restriction on Endianness                               | 212 |

|     | 13.3 | Registe    | er Descriptions                                         | 213 |

|     |      | 13.3.1     | BUSMCNTx : Master Bus Control Register x (x = SYS, DMA) | 213 |

|     |      | 13.3.2     | BUSnERRADD : Bus Error Address Register n (n = 3, 4)    | 213 |

|     |      | 13.3.3     | BUSnERRSTAT : BUS Error Status Register n (n = 3, 4)    | 214 |

|     | 13.4 | Bus Err    | or Monitoring Section                                   | 214 |

|     |      | 13.4.1     | Error Type that Occurs by Bus                           | 214 |

|     |      | 13.4.2     | Operation when a Bus Error Occurs                       | 214 |

|     |      | 13.4.3     | Conditions for issuing illegal Address Access Errors    | 215 |

|     | 13.5 | Referer    | nces                                                    | 215 |

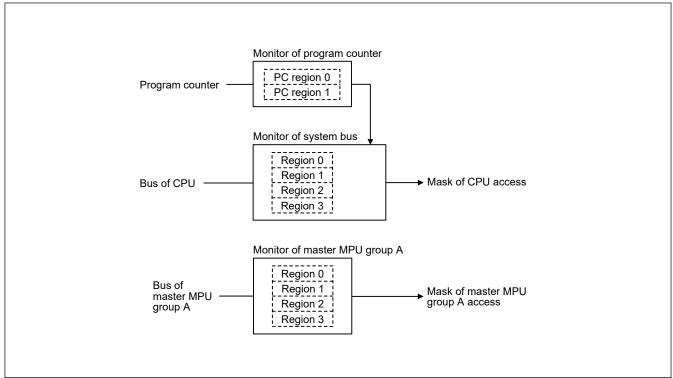

| 14. | Me   | mory Pro   | tection Unit (MPU)                                      | 216 |

|     | 14.1 | -          | ew                                                      |     |

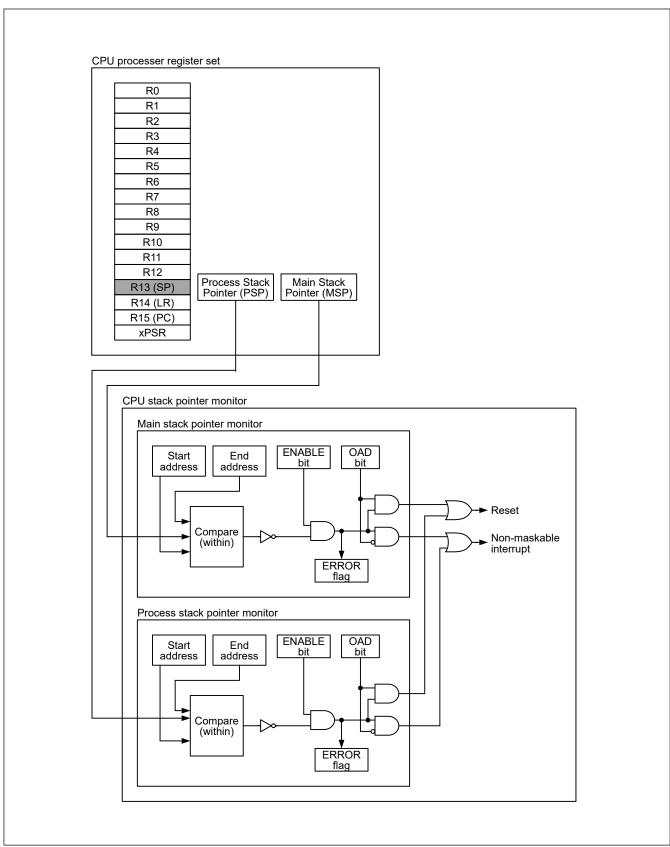

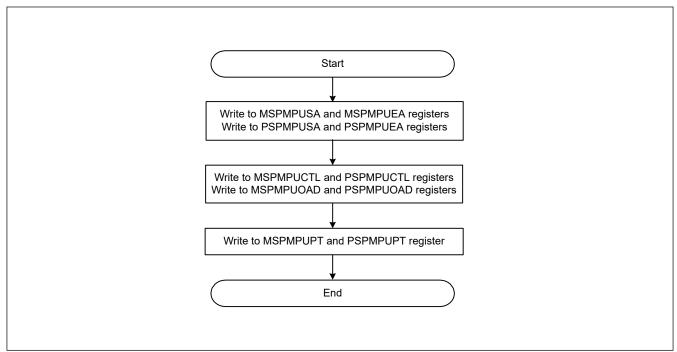

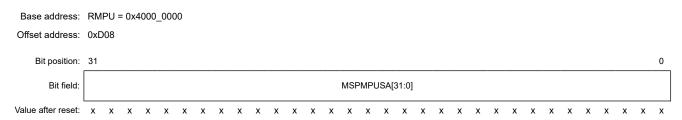

|     | 14.2 | CPU St     | ack Pointer Monitor                                     | 216 |

|     |      | 14.2.1     | Protecting the Registers                                | 219 |

|     |      | 14.2.2     | Overflow and Underflow Errors                           | 219 |

|     |      | 14.2.3     | Register Descriptions                                   | 219 |

|     | 14.3 | Arm MF     | PU                                                      | 223 |

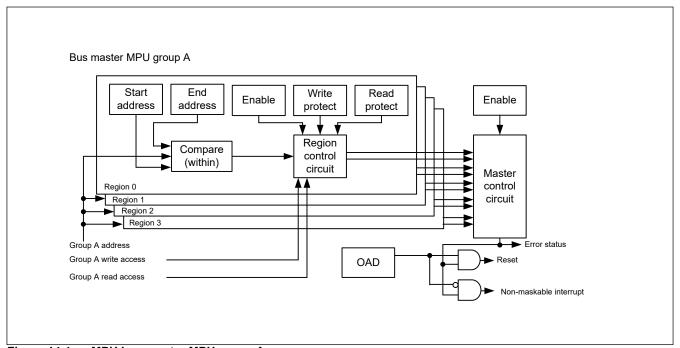

|     | 14.4 | Bus Ma     | ster MPU                                                | 223 |

|     |      | 14.4.1     | Register Descriptions                                   | 224 |

|     |      | 14.4.2     | Operation                                               | 228 |

|     | 14.5 | Bus Sla    | ave MPU                                                 |     |

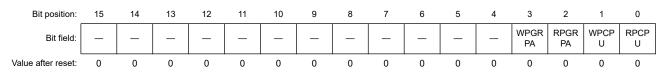

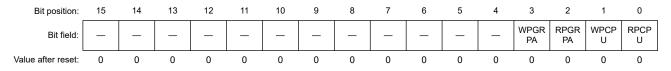

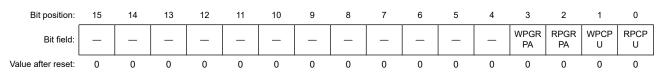

|     |      | 14.5.1     | Register Descriptions                                   | 232 |

|     |      | 14.5.2     | Functions                                               | 237 |

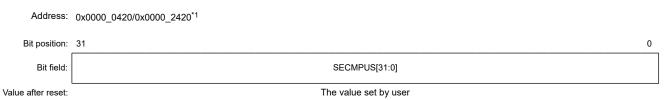

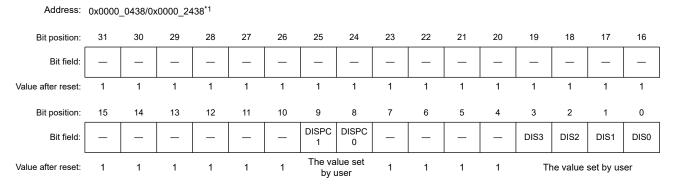

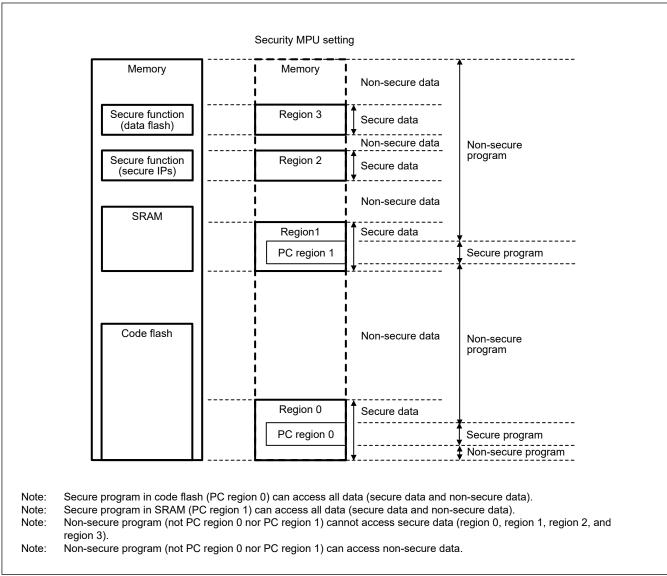

| 14.6     | Security MPU                                               | 237 |

|----------|------------------------------------------------------------|-----|

| 14       | 4.6.1 Register Descriptions (Option-Setting Memory)        | 238 |

| 14       | 4.6.2 Memory Protection                                    | 243 |

| 14.7     | Usage Notes                                                | 244 |

| 14       | 1.7.1 Notes on the Use of a Debugger                       | 244 |

| 14.8     | References                                                 | 244 |

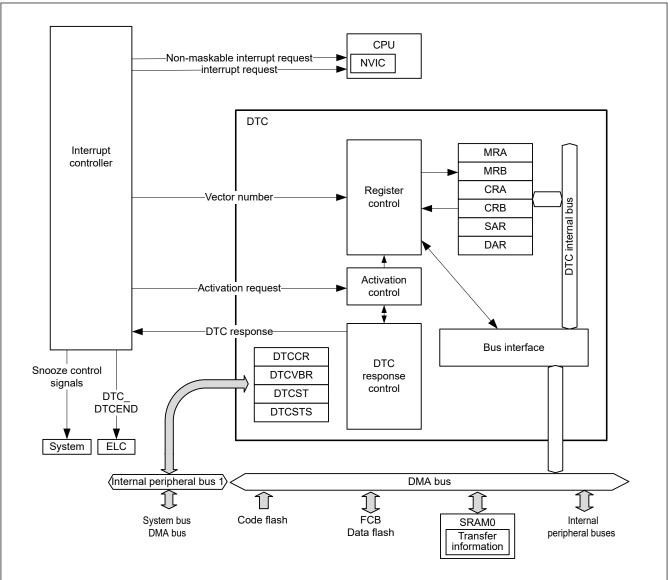

| 15. Data | ı Transfer Controller (DTC)                                | 245 |

| 15.1     | Overview                                                   | 245 |

| 15.2     | Register Descriptions                                      | 246 |

| 15       | 5.2.1 MRA: DTC Mode Register A                             | 246 |

| 15       | 5.2.2 MRB : DTC Mode Register B                            | 247 |

| 15       | 5.2.3 SAR : DTC Transfer Source Register                   | 248 |

| 15       | 5.2.4 DAR : DTC Transfer Destination Register              | 249 |

| 15       | 5.2.5 CRA : DTC Transfer Count Register A                  | 249 |

| 15       | 5.2.6 CRB : DTC Transfer Count Register B                  | 250 |

| 15       | 5.2.7 DTCCR : DTC Control Register                         | 250 |

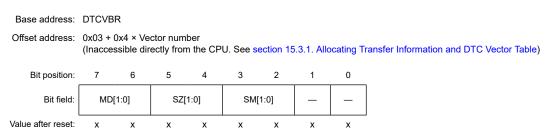

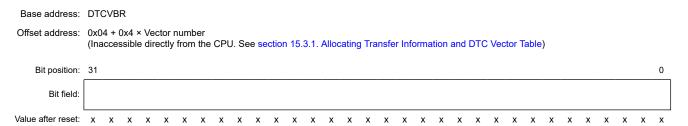

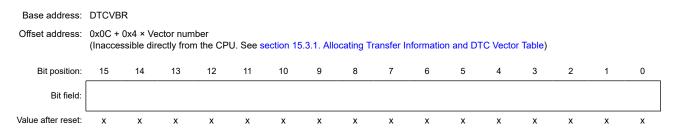

| 15       | 5.2.8 DTCVBR : DTC Vector Base Register                    | 250 |

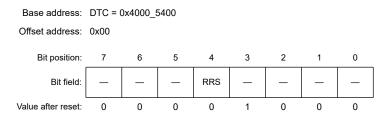

| 15       | 5.2.9 DTCST : DTC Module Start Register                    | 251 |

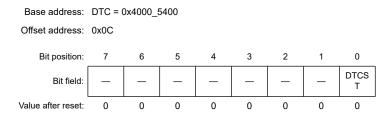

| 15       | 5.2.10 DTCSTS : DTC Status Register                        | 251 |

| 15.3     | Activation Sources                                         | 252 |

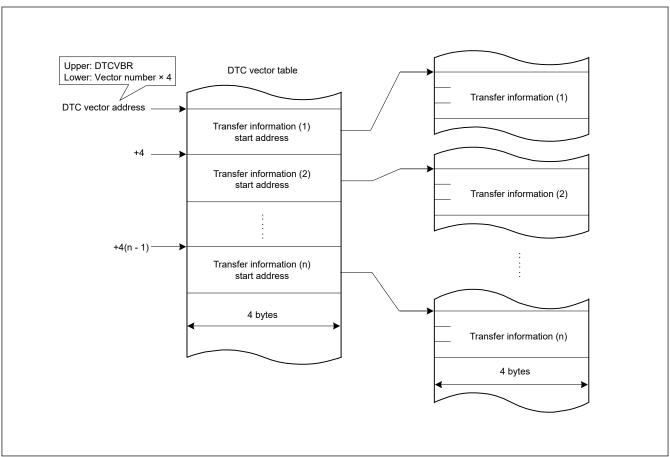

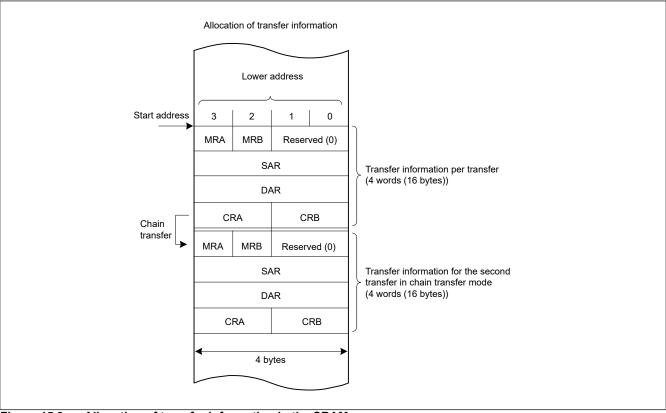

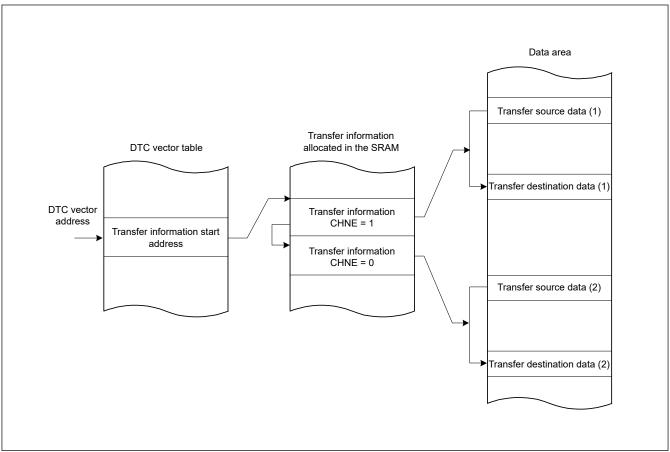

| 15       | 5.3.1 Allocating Transfer Information and DTC Vector Table | 252 |

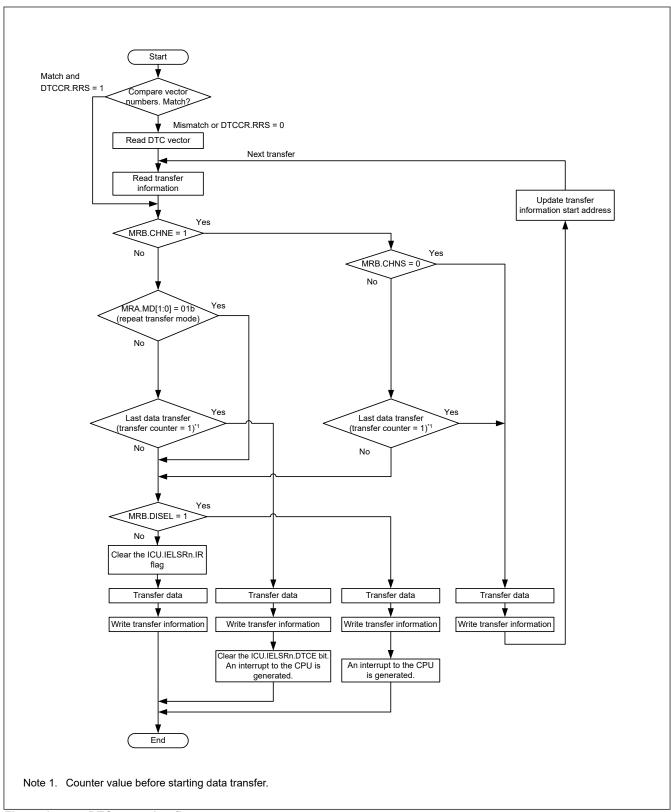

| 15.4     | Operation                                                  | 254 |

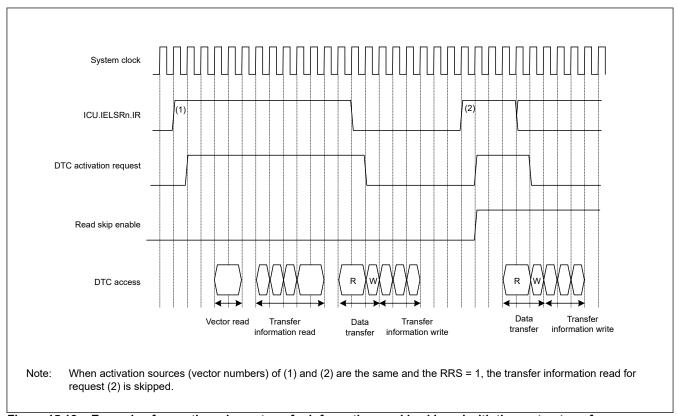

| 15       | 5.4.1 Transfer Information Read Skip Function              | 256 |

| 15       | 5.4.2 Transfer Information Write-Back Skip Function        | 256 |

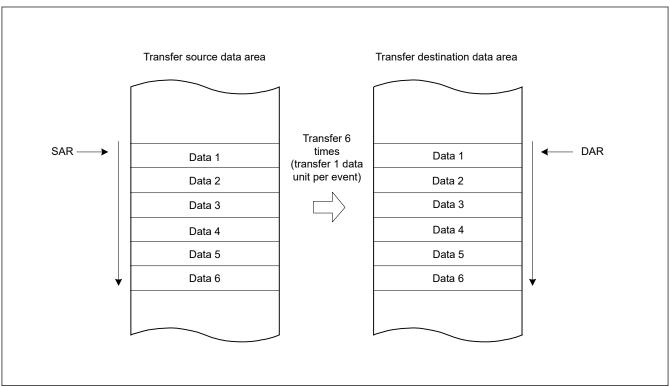

| 15       | 5.4.3 Normal Transfer Mode                                 | 257 |

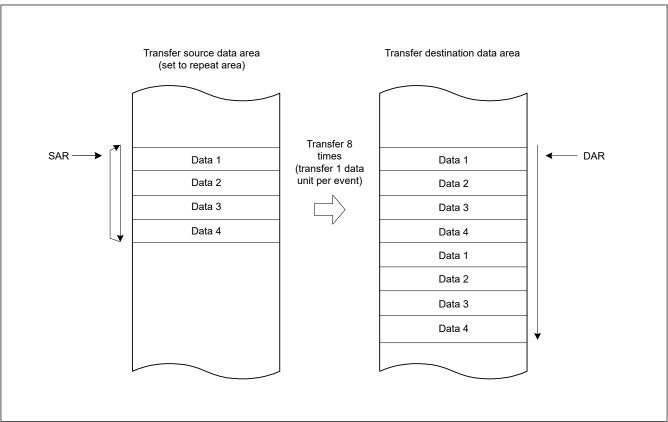

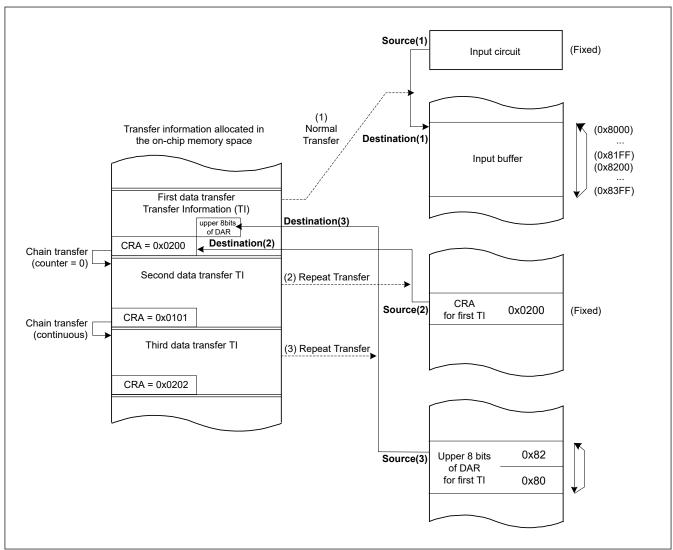

| 15       | 5.4.4 Repeat Transfer Mode                                 | 258 |

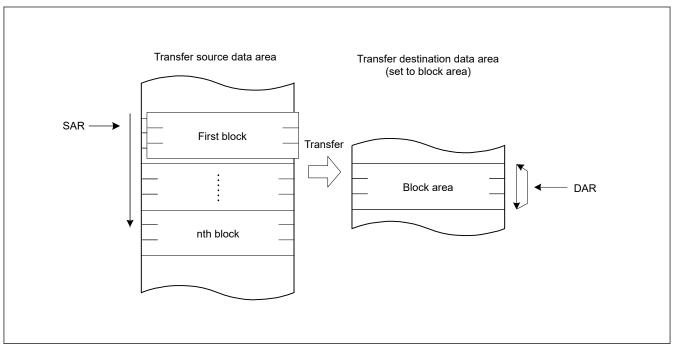

| 15       | 5.4.5 Block Transfer Mode                                  | 259 |

| 15       | 5.4.6 Chain Transfer                                       | 260 |

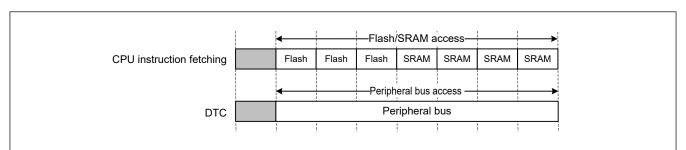

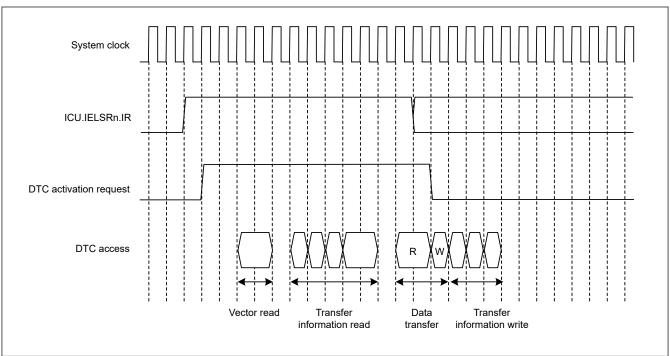

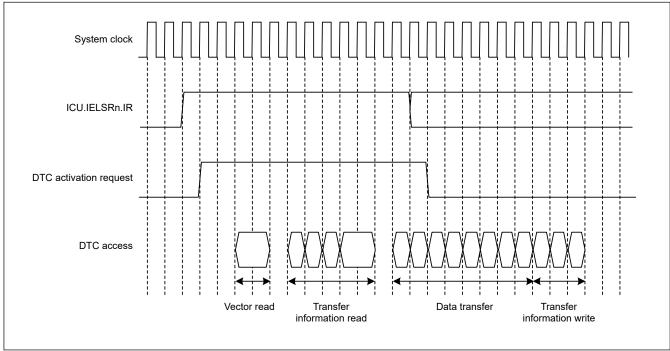

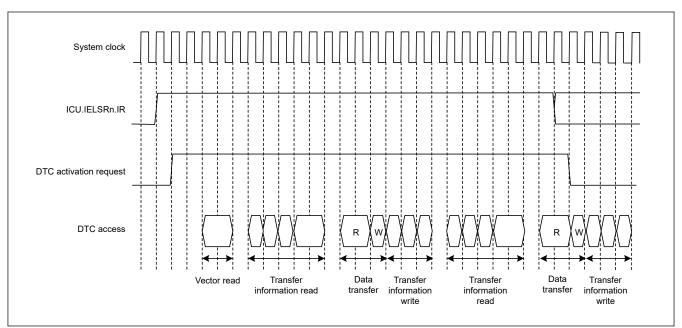

| 15       | 5.4.7 Operation Timing                                     | 261 |

| 15       | 5.4.8 Execution Cycles of DTC                              | 263 |

| 15       | 5.4.9 DTC Bus Mastership Release Timing                    | 264 |

| 15.5     | DTC Setting Procedure                                      | 264 |

| 15.6     | Examples of DTC Usage                                      | 265 |

| 15       | 5.6.1 Normal Transfer                                      | 265 |

| 15       | 5.6.2 Chain transfer                                       | 265 |

| 15       | 5.6.3 Chain Transfer when Counter = 0                      | 267 |

| 15.7     | Interrupt                                                  | 269 |

| 15       | 5.7.1 Interrupt Sources                                    | 269 |

| 15.8     | Event Link                                                 | 269 |

| 15.9     | Low Power Consumption Function                             | 269 |

|     | 15.10 Usage  | Notes                                                                               | 270 |

|-----|--------------|-------------------------------------------------------------------------------------|-----|

|     | 15.10.1      | Transfer Information Start Address                                                  | 270 |

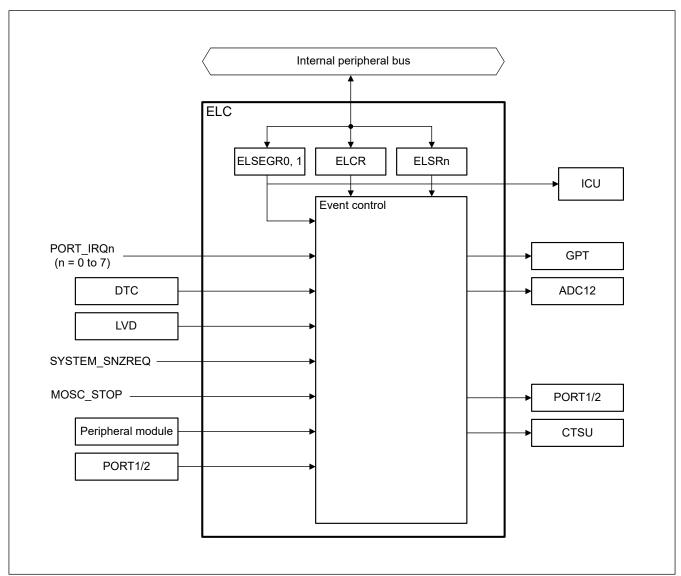

| 16. | Event Link ( | Controller (ELC)                                                                    | 271 |

|     | 16.1 Overvie | ew                                                                                  | 271 |

|     | 16.2 Registe | er Descriptions                                                                     | 272 |

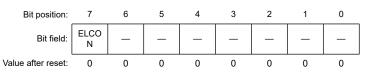

|     | 16.2.1       | ELCR : Event Link Controller Register                                               | 272 |

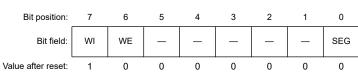

|     | 16.2.2       | ELSEGRn : Event Link Software Event Generation Register n (n = 0, 1)                | 272 |

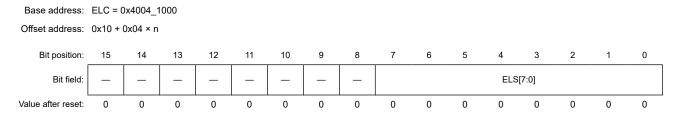

|     | 16.2.3       | ELSRn : Event Link Setting Register n (n = 0 to 3, 8, 9, 14, 15, 18)                | 273 |

|     | 16.3 Operat  | ion                                                                                 | 276 |

|     | 16.3.1       | Relation between Interrupt Handling and Event Linking                               | 276 |

|     | 16.3.2       | Linking Events                                                                      | 276 |

|     | 16.3.3       | Example of Procedure for Linking Events                                             | 277 |

|     | 16.4 Usage   | Notes                                                                               | 277 |

|     | 16.4.1       | Linking DTC Transfer End Signals as Events                                          | 277 |

|     | 16.4.2       | Setting Clocks                                                                      | 277 |

|     | 16.4.3       | Module-Stop Function Setting                                                        | 277 |

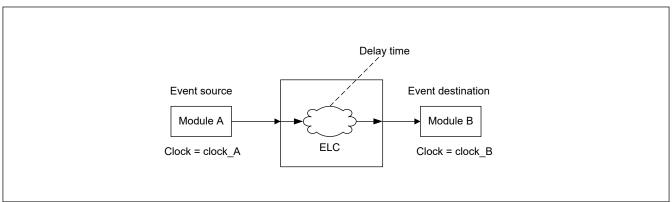

|     | 16.4.4       | ELC Delay Time                                                                      | 277 |

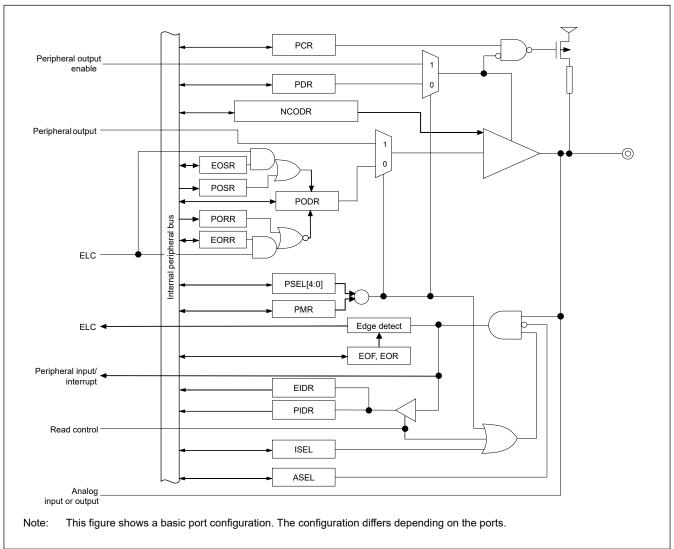

| 17. | I/O Ports    |                                                                                     | 279 |

|     |              | ew                                                                                  |     |

|     | 17.2 Registe | er Descriptions                                                                     | 281 |

|     | 17.2.1       | PCNTR1/PODR/PDR : Port Control Register 1                                           | 281 |

|     | 17.2.2       | PCNTR2/EIDR/PIDR : Port Control Register 2                                          | 282 |

|     | 17.2.3       | PCNTR3/PORR/POSR : Port Control Register 3                                          | 283 |

|     | 17.2.4       | PCNTR4/EORR/EOSR : Port Control Register 4                                          | 283 |

|     | 17.2.5       | PmnPFS/PmnPFS_HA/PmnPFS_BY: Port mn Pin Function Select Register (m = n = 00 to 15) |     |

|     | 17.2.6       | PWPR : Write-Protect Register                                                       | 286 |

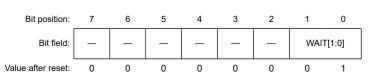

|     | 17.2.7       | PRWCNTR : Port Read Wait Control Register                                           | 287 |

|     | 17.3 Operat  | ion                                                                                 | 287 |

|     | 17.3.1       | General I/O Ports                                                                   | 287 |

|     | 17.3.2       | Port Function Select                                                                | 287 |

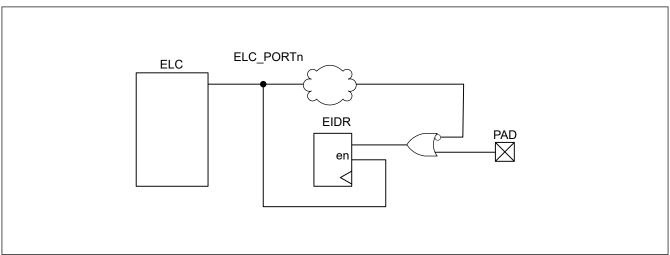

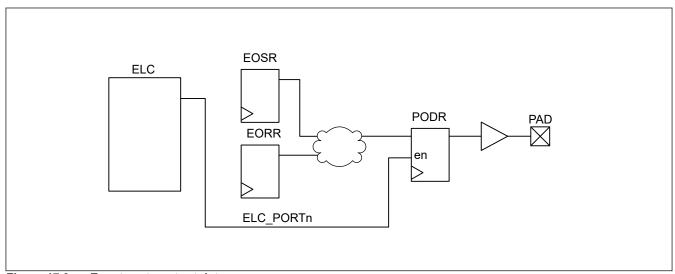

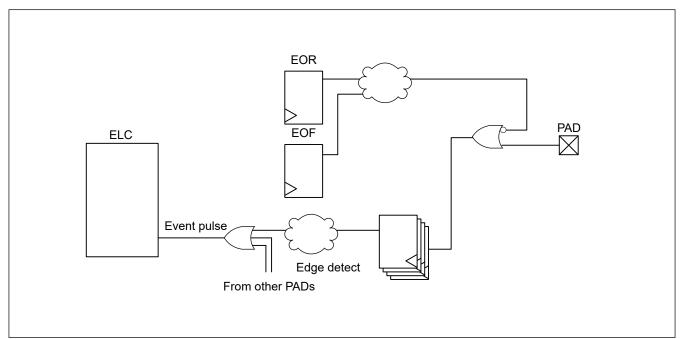

|     | 17.3.3       | Port Group Function for ELC                                                         | 288 |

|     | 17.3.4       | Wait Function for Port Read                                                         | 289 |

|     | 17.4 Handlir | ng of Unused Pins                                                                   | 290 |

|     | 17.5 Usage   | Notes                                                                               | 290 |

|     | 17.5.1       | Procedure for Specifying the Pin Functions                                          | 290 |

|     | 17.5.2       | Procedure for Using Port Group Input                                                | 291 |

|     | 17.5.3       | Port Output Data Register (PODR) Summary                                            | 291 |

|     | 17.5.4       | Notes on Using Analog Functions                                                     | 291 |

|     | 17.6 Periphe | eral Select Settings for Each Product                                               | 291 |

| 18. | Key                     | Interru | pt Function (KINT)                                                 | 295 |

|-----|-------------------------|---------|--------------------------------------------------------------------|-----|

|     | 18.1 Overvie            |         | ew                                                                 | 295 |

|     | 18.2                    | Regist  | er Descriptions                                                    | 295 |

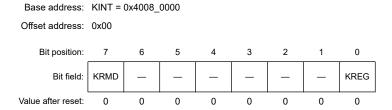

|     | 18                      | 3.2.1   | KRCTL : Key Return Control Register                                | 295 |

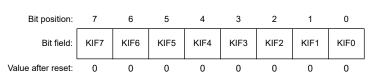

|     | 18                      | 3.2.2   | KRF : Key Return Flag Register                                     | 296 |

|     | 18                      | 3.2.3   | KRM : Key Return Mode Register                                     | 296 |

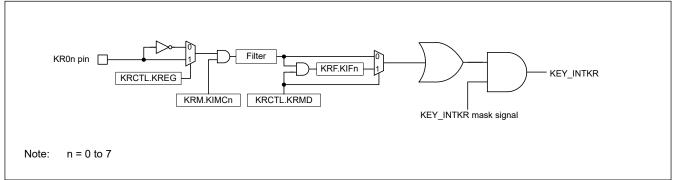

|     | 18.3                    | Opera   | tion                                                               | 296 |

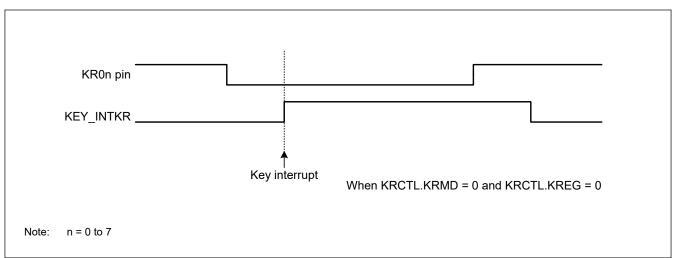

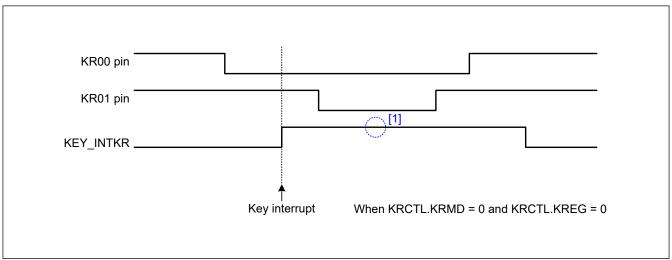

|     | 18                      | 3.3.1   | Operation When Not Using the Key Interrupt Flags (KRCTL.KRMD = 0)  | 296 |

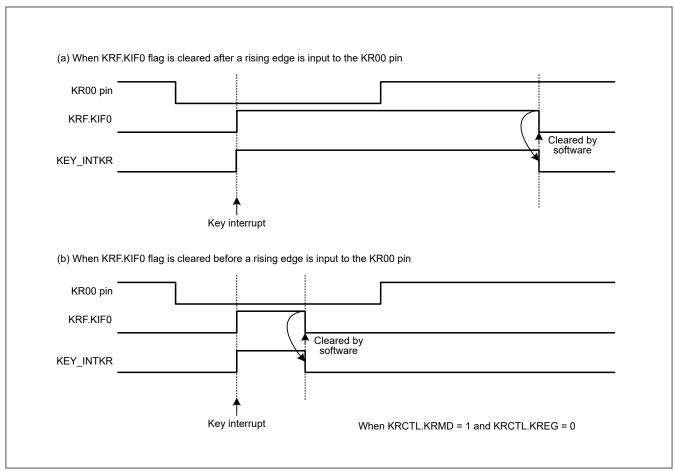

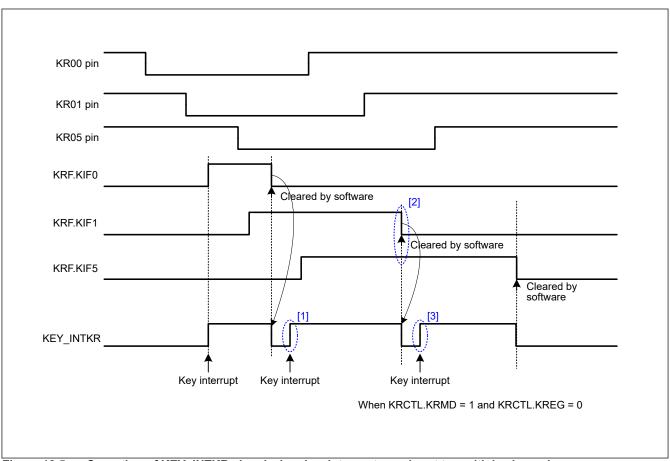

|     | 18                      | 3.3.2   | Operation When Using the Key Interrupt Flags (KRCTL.KRMD = 1)      | 297 |

|     | 18.4                    | Usage   | Notes                                                              | 299 |

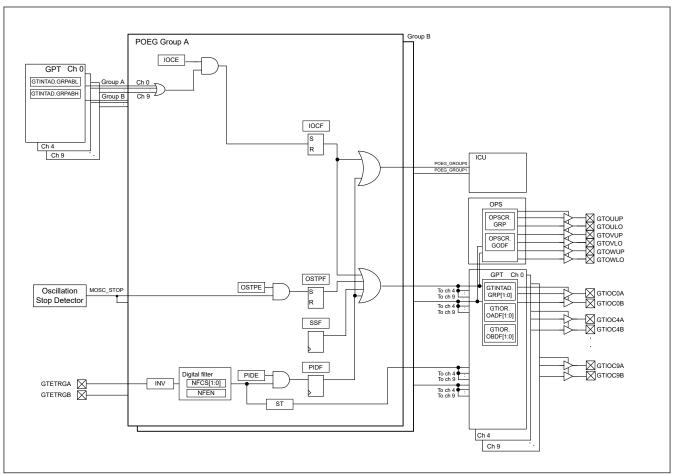

| 19. | Port                    | Output  | t Enable for GPT (POEG)                                            | 300 |

|     | 19.1                    | -       | ew                                                                 |     |

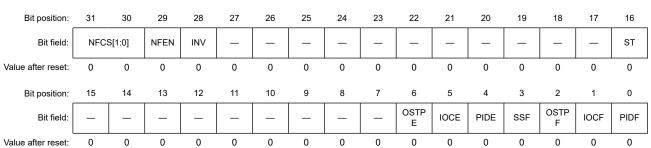

|     | 19.2                    | Regist  | er Descriptions                                                    | 301 |

|     |                         | 9.2.1   | POEGGn : POEG Group n Setting Register (n = A, B)                  |     |

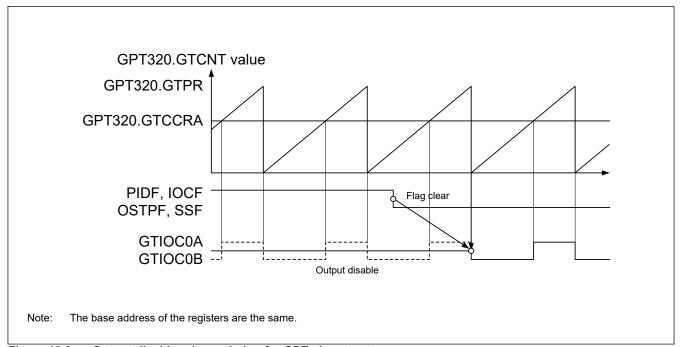

|     | 19.3                    | Output  | t-Disable Control Operation                                        |     |

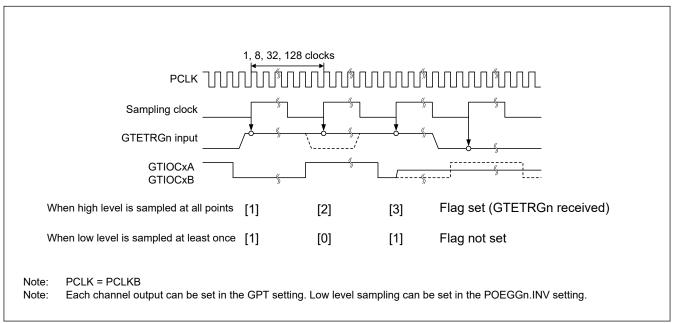

|     | 19                      | 9.3.1   | Pin Input Level Detection Operation                                | 303 |

|     | 19                      | 9.3.2   | Output-Disable Requests from the GPT                               |     |

|     | 19                      | 9.3.3   | Output-Disable Control Using Detection of Stopped Oscillation      | 303 |

|     | 19                      | 9.3.4   | Output-Disable Control Using Registers                             | 303 |

|     | 19                      | 9.3.5   | Release from Output-Disable                                        | 304 |

|     | 19.4                    | Interru | pt Sources                                                         | 304 |

|     | 19.5                    | Extern  | al Trigger Output to the GPT                                       | 305 |

|     | 19.6                    | Usage   | Notes                                                              | 305 |

|     | 19                      | 9.6.1   | Transition to Software Standby Mode                                | 305 |

|     | 19                      | 9.6.2   | Specifying Pins Associated with the GPT                            | 305 |

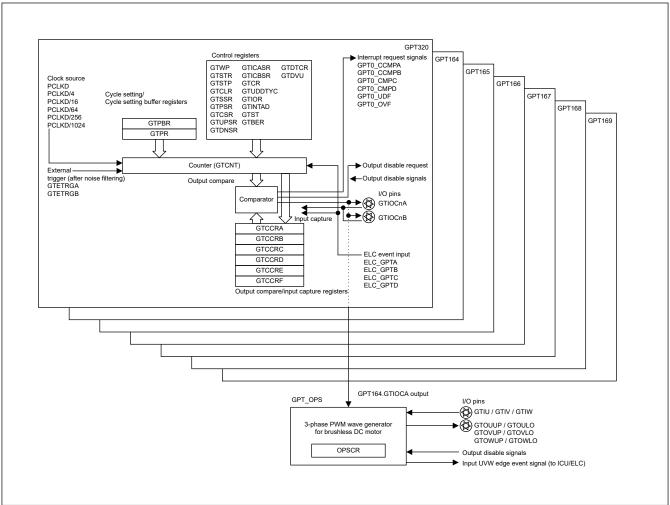

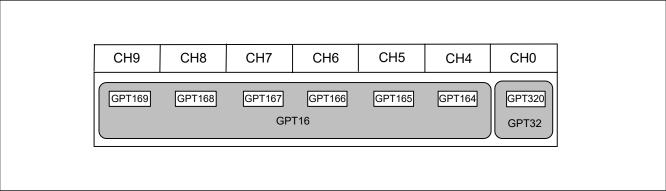

| 20  | Gon                     | oral DW | /M Timer (GPT)                                                     | 306 |

|     | General PWM Timer (GPT) |         |                                                                    |     |

|     | 20.1                    |         | er Descriptions                                                    |     |

|     |                         | ).2.1   | GTWP : General PWM Timer Write-Protection Register                 |     |

|     |                         | 0.2.2   | GTSTR : General PWM Timer Software Start Register                  |     |

|     |                         | 0.2.3   | GTSTP : General PWM Timer Software Stop Register                   |     |

|     |                         | 0.2.4   | GTCLR : General PWM Timer Software Clear Register                  |     |

|     |                         | 0.2.5   | GTSSR : General PWM Timer Start Source Select Register             |     |

|     |                         | 0.2.6   | GTPSR : General PWM Timer Stop Source Select Register              |     |

|     |                         | 0.2.7   | GTCSR : General PWM Timer Clear Source Select Register             |     |

|     |                         | 0.2.8   | GTUPSR : General PWM Timer Up Count Source Select Register         |     |

|     |                         | 0.2.9   | GTDNSR : General PWM Timer Down Count Source Select Register       |     |

|     |                         | 0.2.10  | GTICASR : General PWM Timer Input Capture Source Select Register A |     |

|     |                         | 0.2.11  | GTICBSR : General PWM Timer Input Capture Source Select Register B |     |

| 2    | 20.2.12   | GTCR : General PWM Timer Control Register                              | 330 |

|------|-----------|------------------------------------------------------------------------|-----|

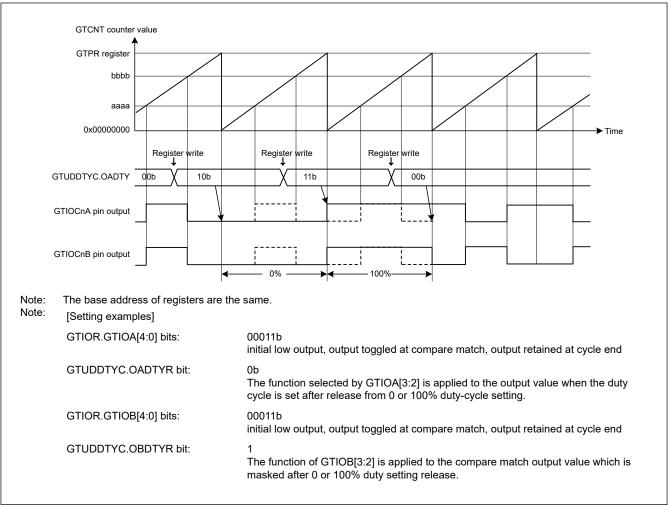

| 2    | 20.2.13   | GTUDDTYC : General PWM Timer Count Direction and Duty Setting Register | 331 |

| 2    | 20.2.14   | GTIOR : General PWM Timer I/O Control Register                         | 333 |

| 2    | 20.2.15   | GTINTAD : General PWM Timer Interrupt Output Setting Register          | 337 |

| 2    | 20.2.16   | GTST : General PWM Timer Status Register                               | 338 |

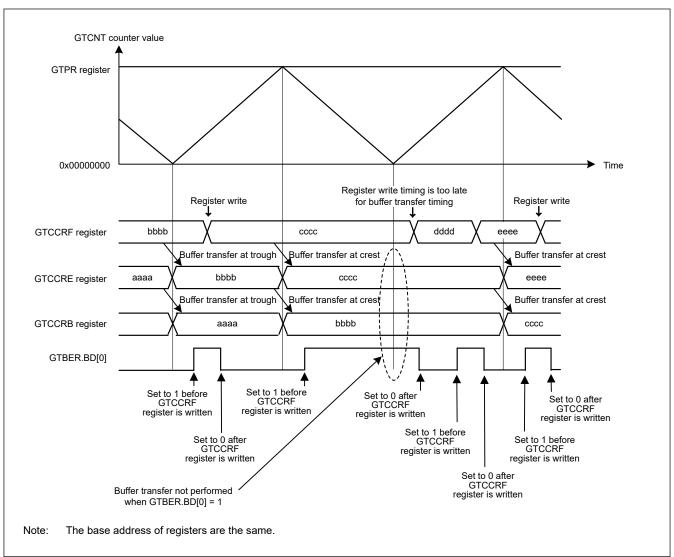

| 2    | 20.2.17   | GTBER : General PWM Timer Buffer Enable Register                       | 342 |

| 2    | 20.2.18   | GTCNT : General PWM Timer Counter                                      | 343 |

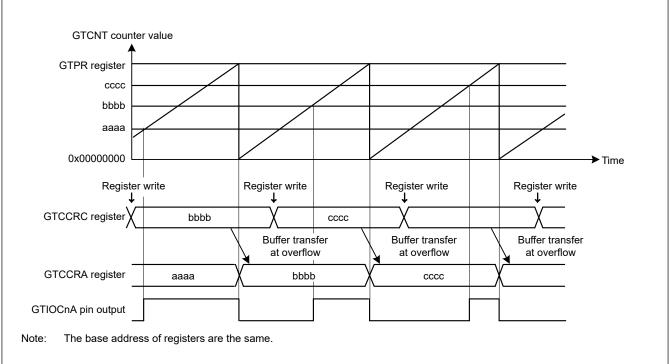

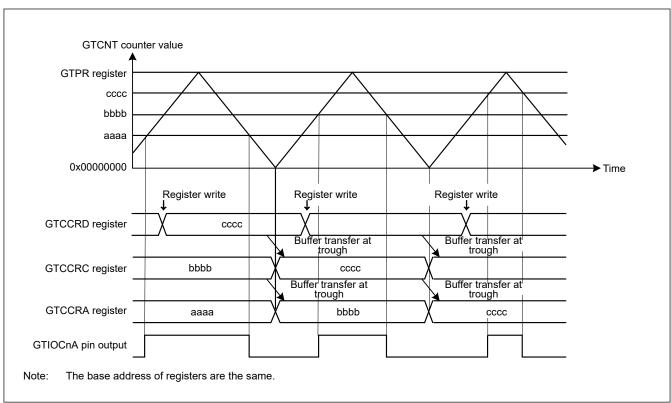

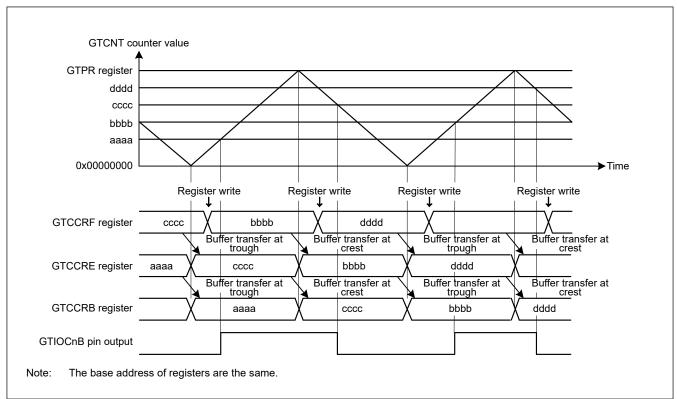

| 2    | 20.2.19   | GTCCRk : General PWM Timer Compare Capture Register k (k = A to F)     | 343 |

| 2    | 20.2.20   | GTPR : General PWM Timer Cycle Setting Register                        | 344 |

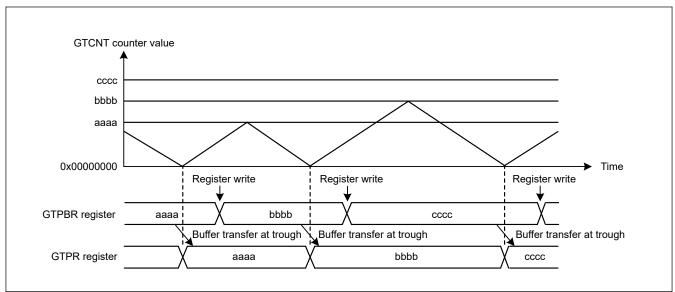

| 2    | 20.2.21   | GTPBR : General PWM Timer Cycle Setting Buffer Register                | 344 |

| 2    | 20.2.22   | GTDTCR : General PWM Timer Dead Time Control Register                  | 344 |

| 2    | 20.2.23   | GTDVU : General PWM Timer Dead Time Value Register U                   | 345 |

| 2    | 20.2.24   | OPSCR : Output Phase Switching Control Register                        | 346 |

| 20.3 | Operat    | ion                                                                    | 348 |

| 2    | 20.3.1    | Basic Operation                                                        | 348 |

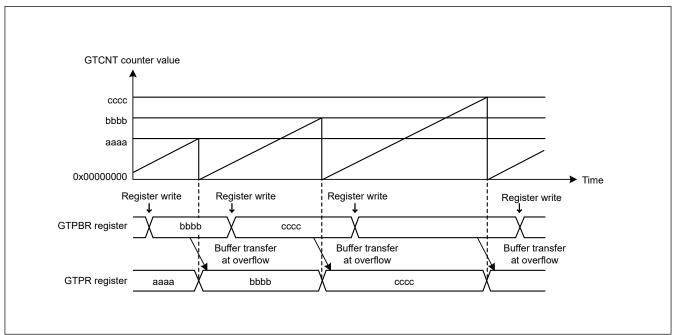

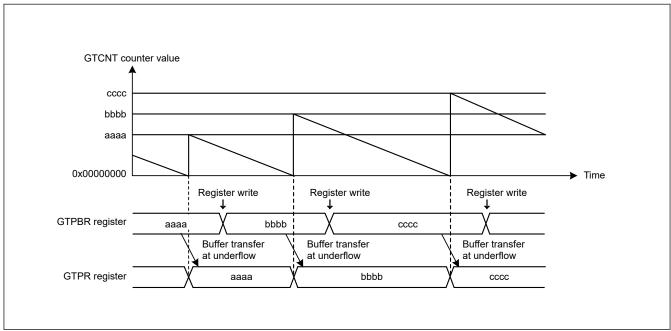

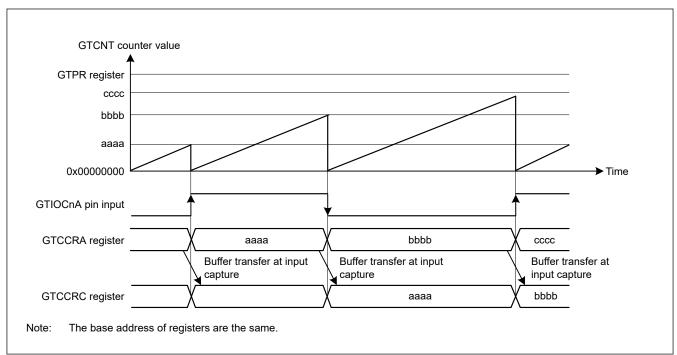

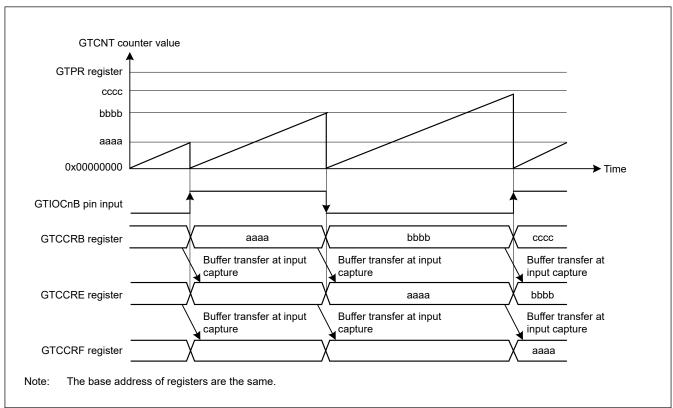

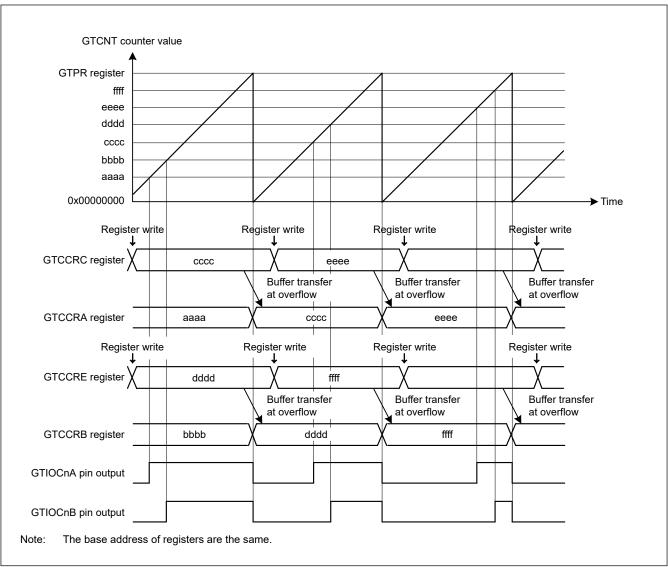

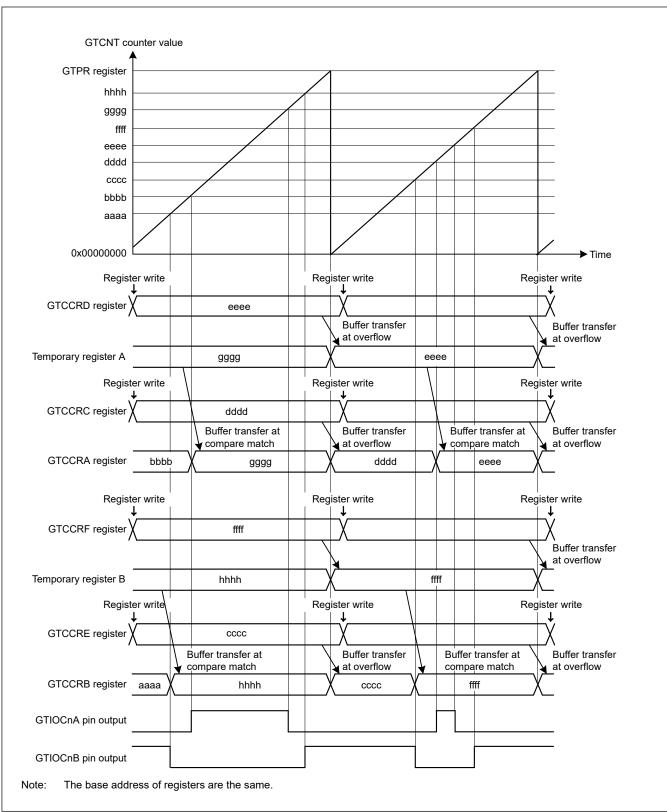

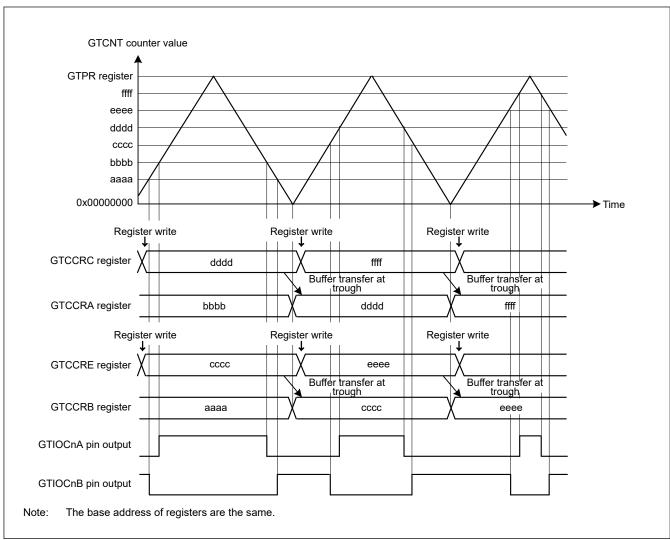

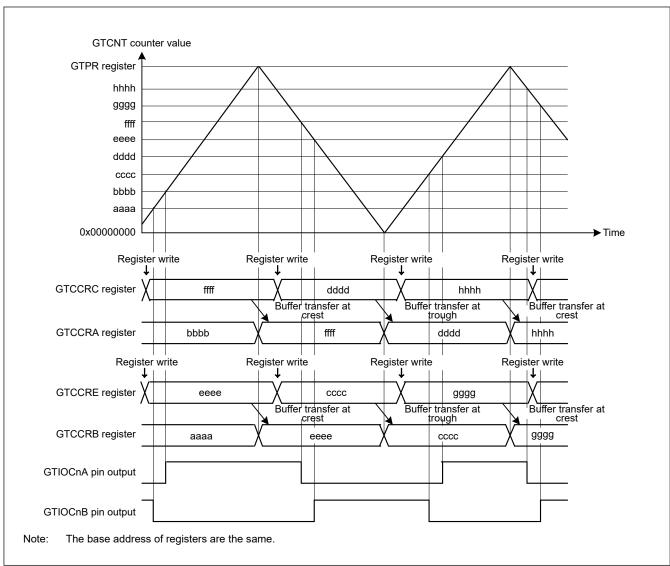

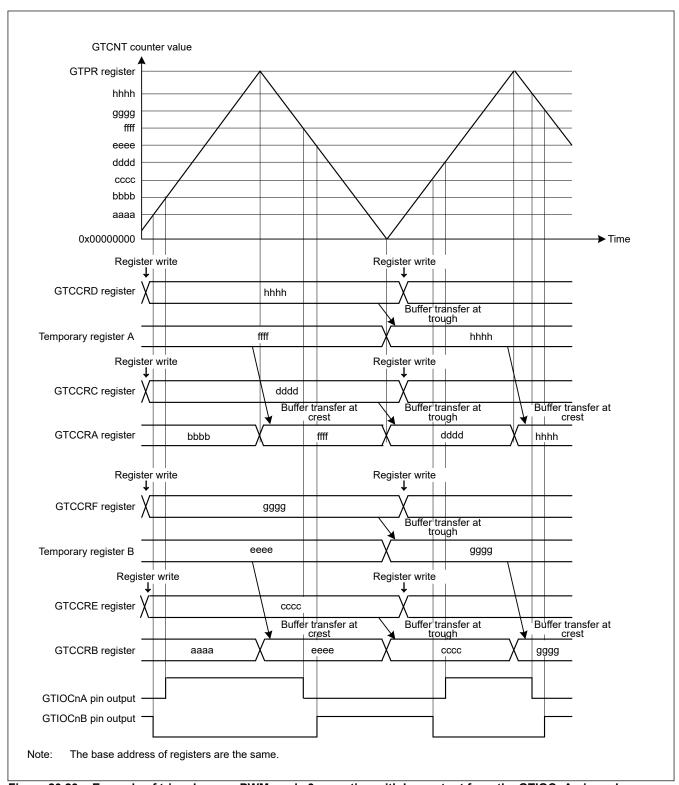

| 2    | 20.3.2    | Buffer Operation                                                       | 356 |

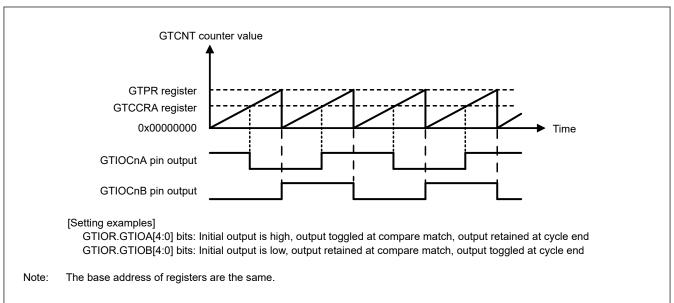

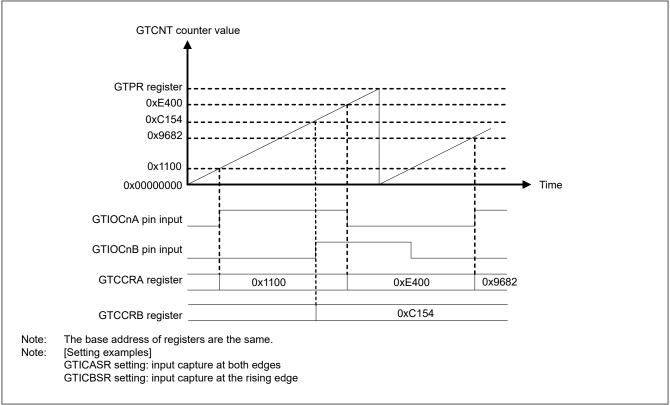

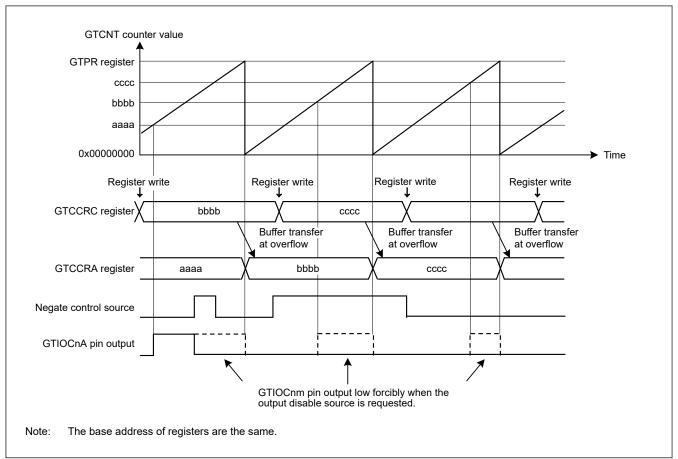

| 2    | 20.3.3    | PWM Output Operating Mode                                              | 363 |

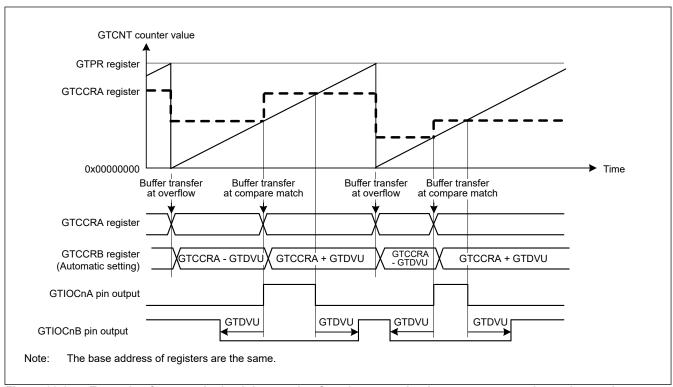

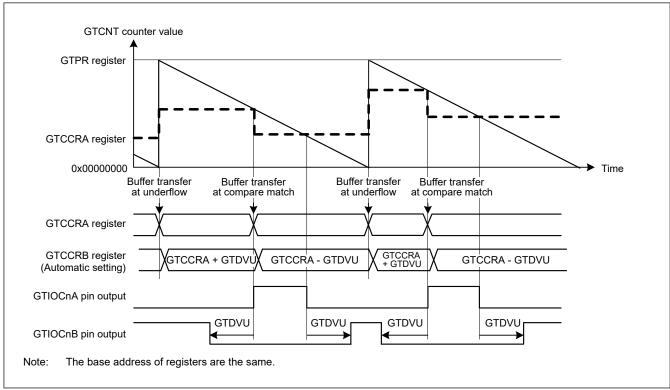

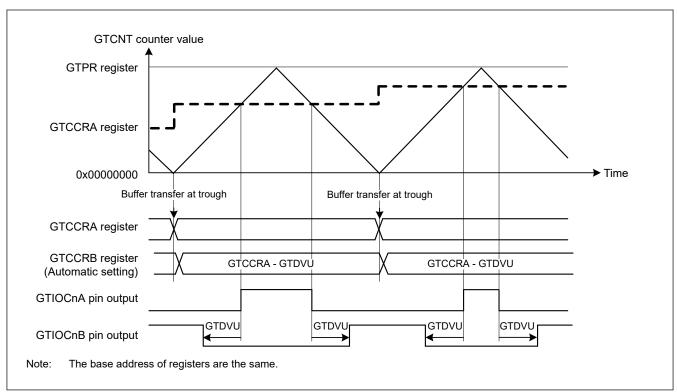

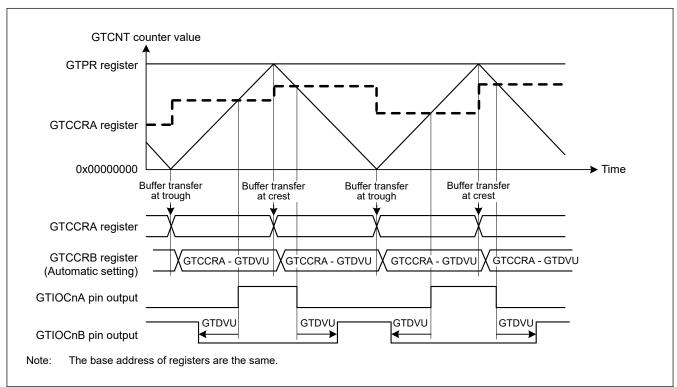

| 2    | 20.3.4    | Automatic Dead Time Setting Function                                   | 373 |

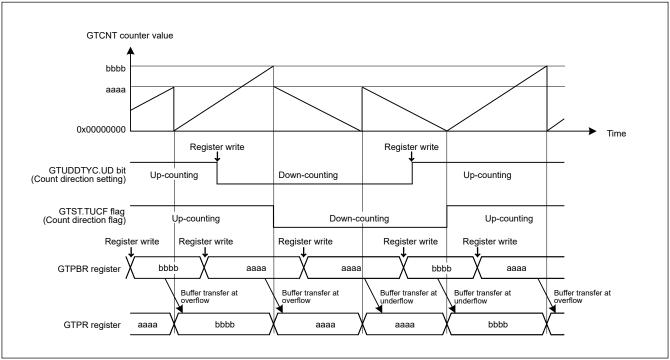

| 2    | 20.3.5    | Count Direction Changing Function                                      | 377 |

| 2    | 20.3.6    | Function of Output Duty 0% and 100%                                    | 377 |

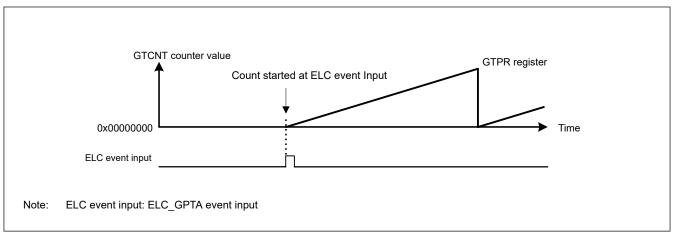

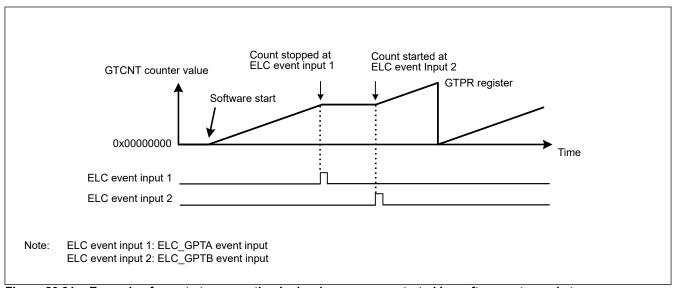

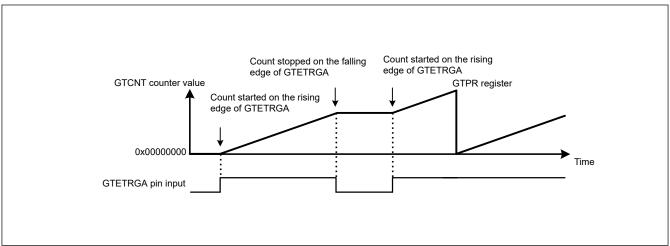

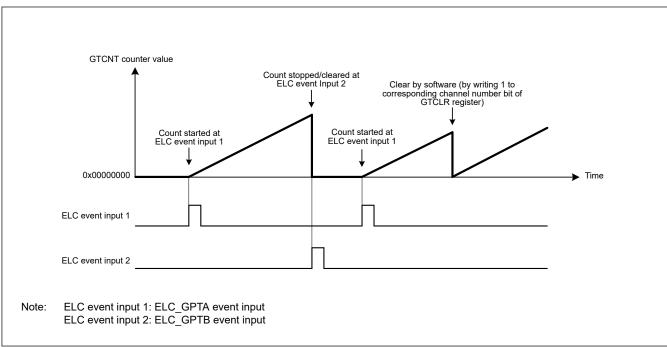

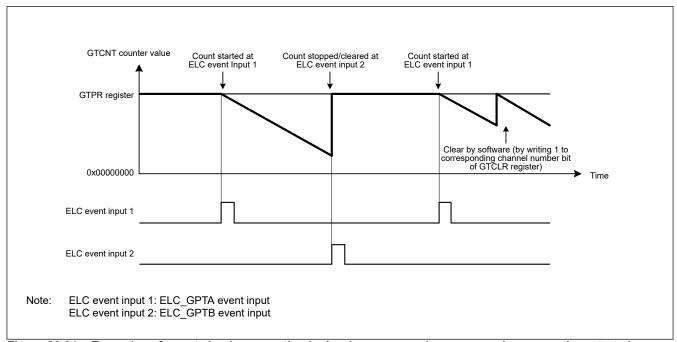

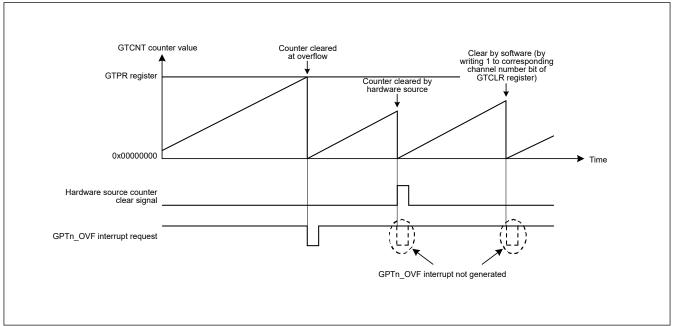

| 2    | 20.3.7    | Hardware Count Start/Count Stop and Clear Operation                    | 379 |

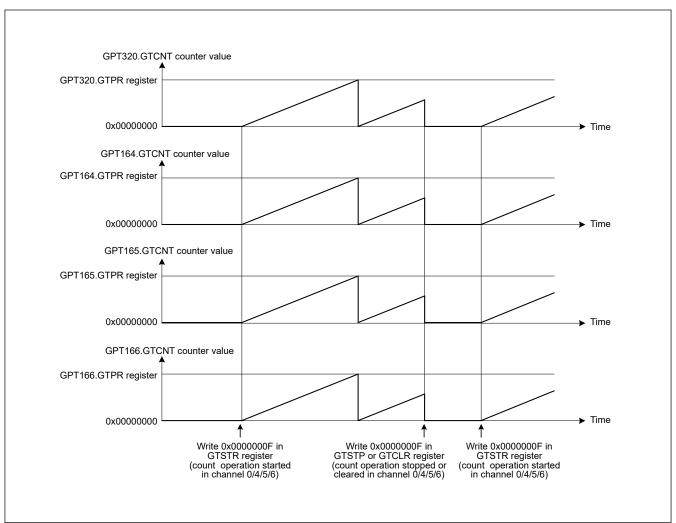

| 2    | 20.3.8    | Synchronized Operation                                                 | 384 |

| 2    | 20.3.9    | PWM Output Operation Examples                                          | 388 |

| 2    | 20.3.10   | Phase Counting Function                                                | 393 |

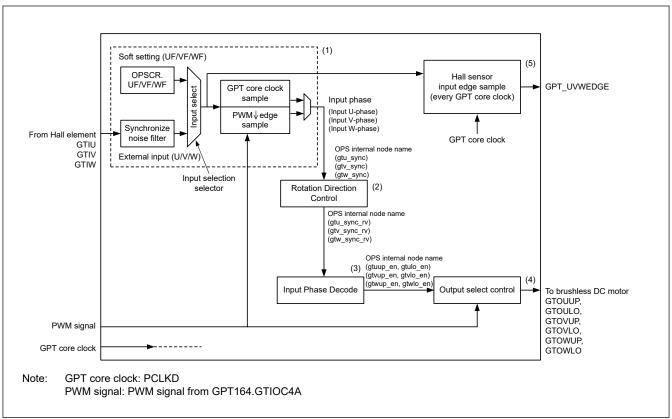

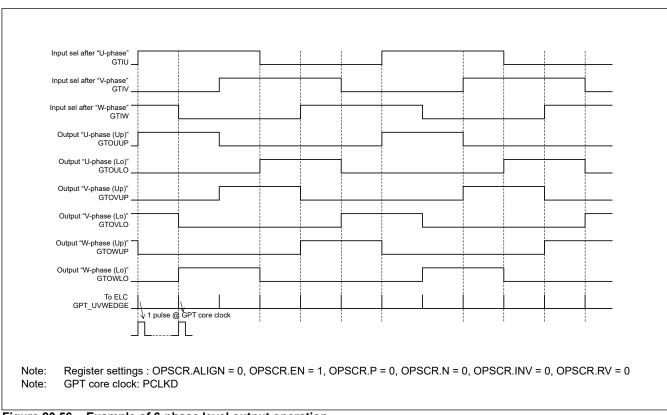

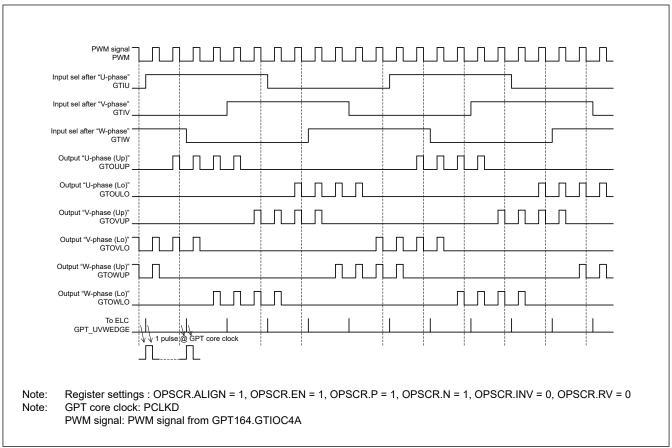

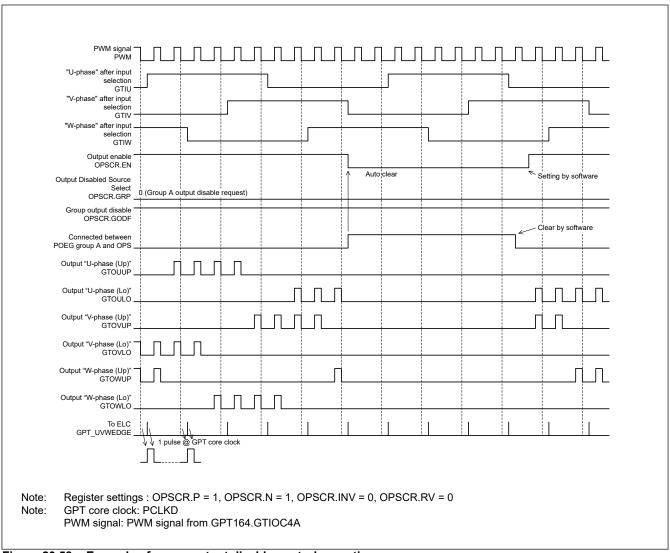

| 2    | 20.3.11   | Output Phase Switching (GPT_OPS)                                       | 403 |

| 20.4 | Interru   | ot Sources                                                             | 410 |

| 2    | 20.4.1    | Interrupt Sources                                                      | 410 |

| 2    | 20.4.2    | DTC Activation                                                         | 412 |

| 20.5 | Operat    | ions Linked by ELC                                                     | 412 |

| 2    | 20.5.1    | Event Signal Output to ELC                                             | 412 |

| 2    | 20.5.2    | Event Signal Inputs from ELC                                           | 412 |

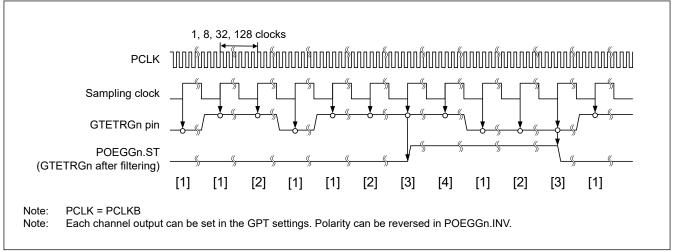

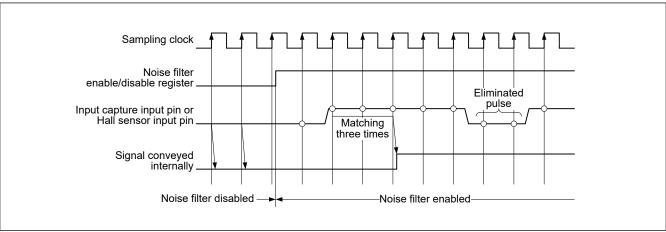

| 20.6 | Noise F   | Filter Function                                                        | 412 |

| 20.7 | Protect   | ion Function                                                           | 413 |

| 2    | 20.7.1    | Write-Protection for Registers                                         | 413 |

| 2    | 20.7.2    | Disabling of Buffer Operation                                          | 413 |

| 2    | 20.7.3    | GTIOCnm Pin Output Negate Control (n = 0, 4 to 9, m = A, B)            | 414 |

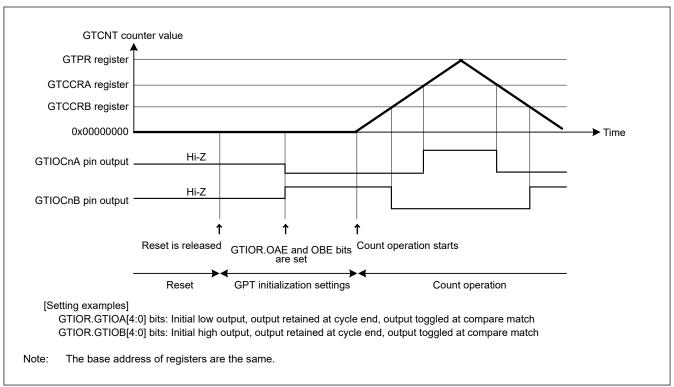

| 20.8 | Initializ | ation Method of Output Pins                                            | 415 |

| 2    | 20.8.1    | Pin Settings after Reset                                               | 415 |

| 2    | 20.8.2    | Pin Initialization Due to Error during Operation                       | 416 |

| 20.9 | Usage     | Notes                                                                  | 416 |

|    | 20.9.1       | Module-Stop Function Setting                                         | 416 |

|----|--------------|----------------------------------------------------------------------|-----|

|    | 20.9.2       | GTCCRn Settings during Compare Match Operation (n = A to F)          | 416 |

|    | 20.9.3       | Setting Range for GTCNT Counter                                      | 417 |

|    | 20.9.4       | Starting and Stopping the GTCNT Counter                              | 417 |

|    | 20.9.5       | Priority Order of Each Event                                         | 417 |

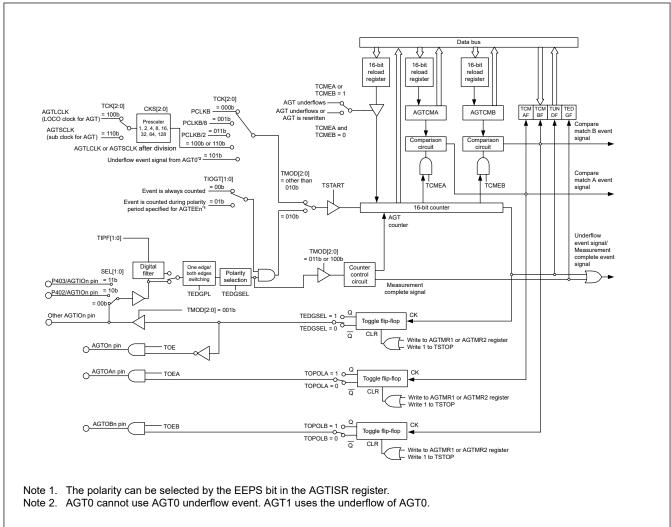

| 21 | . Low Power  | Asynchronous General Purpose Timer (AGT)                             | 419 |

|    | 21.1 Overvi  | ew                                                                   | 419 |

|    | 21.2 Registo | er Descriptions                                                      | 421 |

|    | 21.2.1       | AGT : AGT Counter Register                                           | 421 |

|    | 21.2.2       | AGTCMA : AGT Compare Match A Register                                | 421 |

|    | 21.2.3       | AGTCMB : AGT Compare Match B Register                                | 422 |

|    | 21.2.4       | AGTCR : AGT Control Register                                         | 422 |

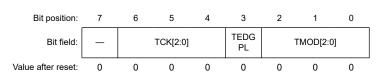

|    | 21.2.5       | AGTMR1 : AGT Mode Register 1                                         | 424 |

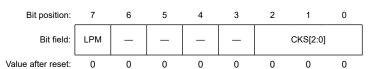

|    | 21.2.6       | AGTMR2 : AGT Mode Register 2                                         | 424 |

|    | 21.2.7       | AGTIOC : AGT I/O Control Register                                    | 426 |

|    | 21.2.8       | AGTISR : AGT Event Pin Select Register                               | 427 |

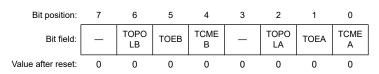

|    | 21.2.9       | AGTCMSR : AGT Compare Match Function Select Register                 | 428 |

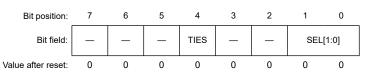

|    | 21.2.10      | AGTIOSEL : AGT Pin Select Register                                   | 428 |

|    | 21.3 Operat  | tion                                                                 | 429 |

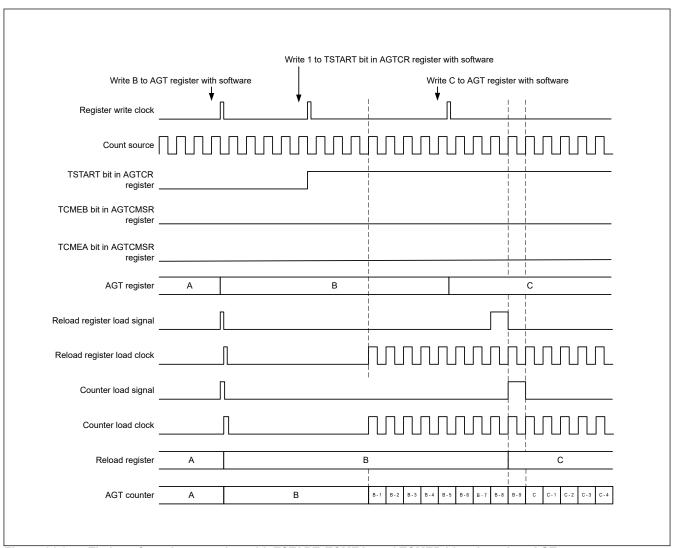

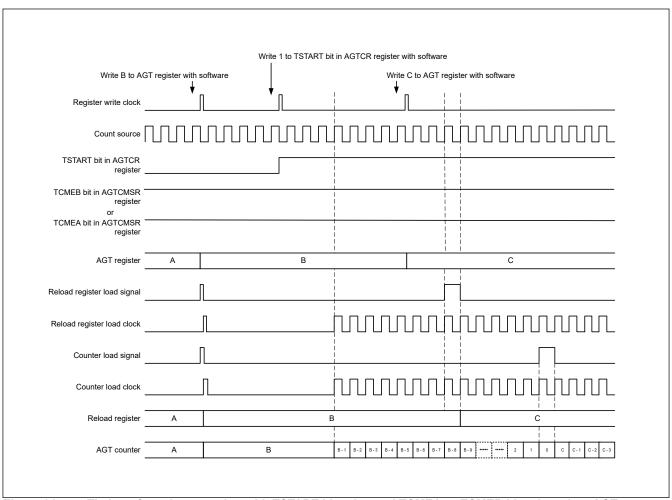

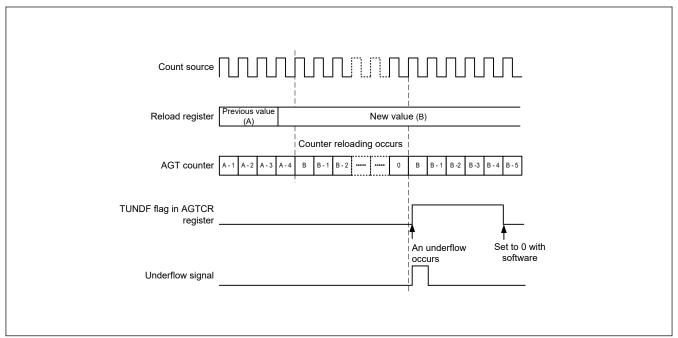

|    | 21.3.1       | Reload Register and Counter Rewrite Operation                        | 429 |

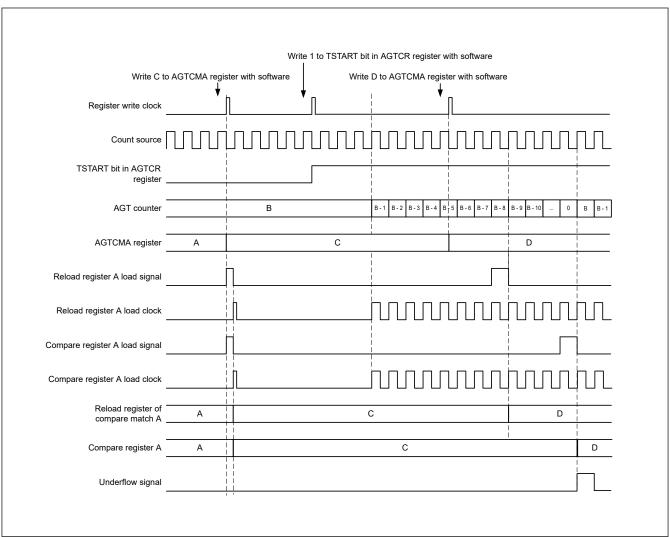

|    | 21.3.2       | Reload Register and AGT Compare Match A/B Register Rewrite Operation | 431 |

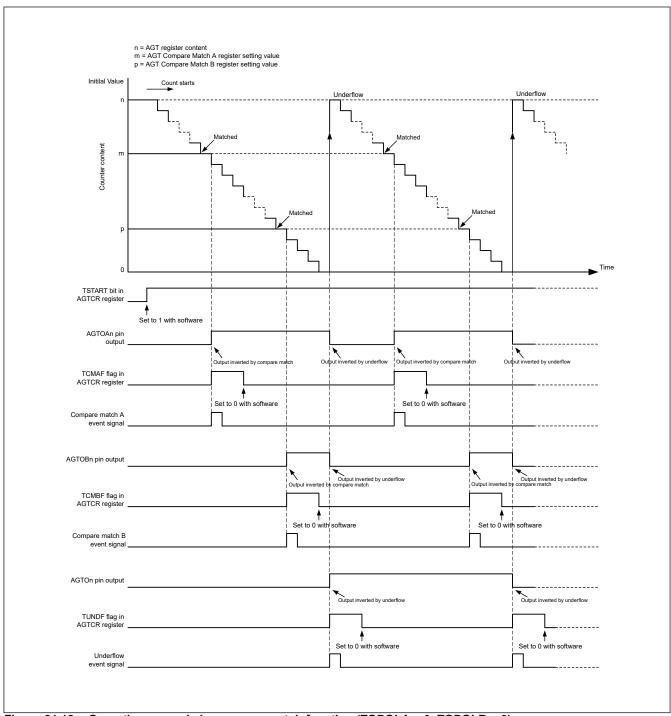

|    | 21.3.3       | Timer Mode                                                           | 432 |

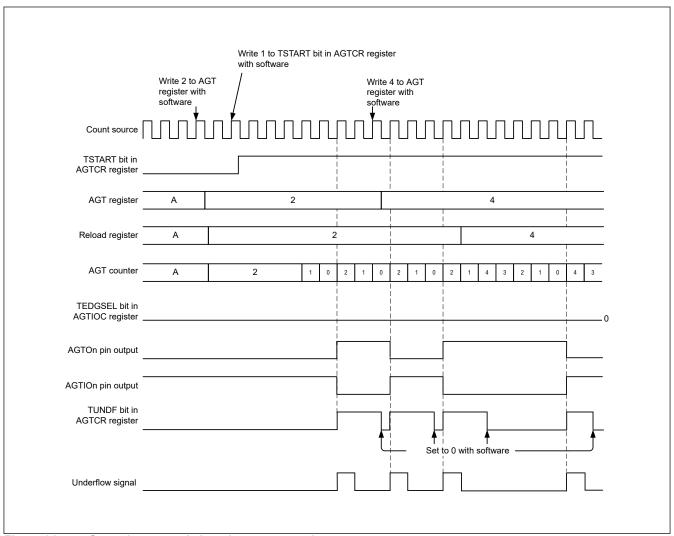

|    | 21.3.4       | Pulse Output Mode                                                    | 433 |

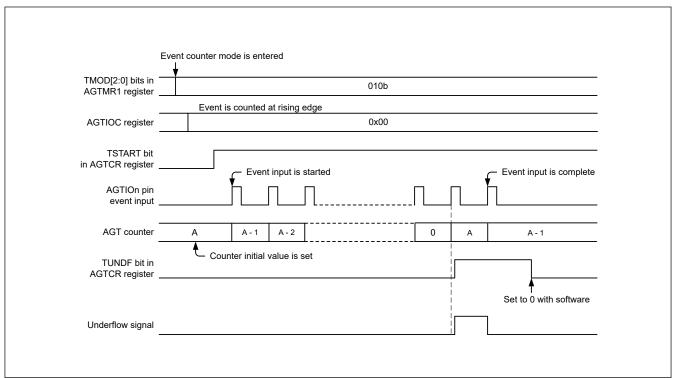

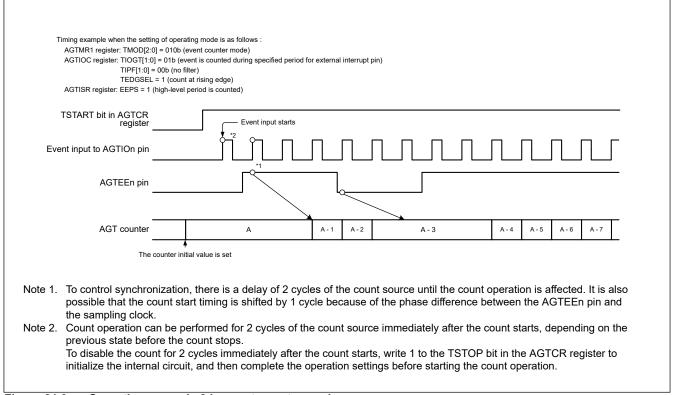

|    | 21.3.5       | Event Counter Mode                                                   | 434 |

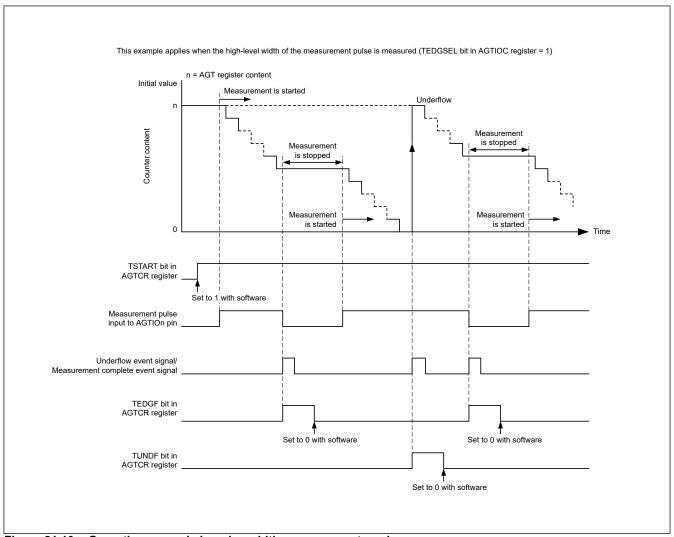

|    | 21.3.6       | Pulse Width Measurement Mode                                         | 435 |

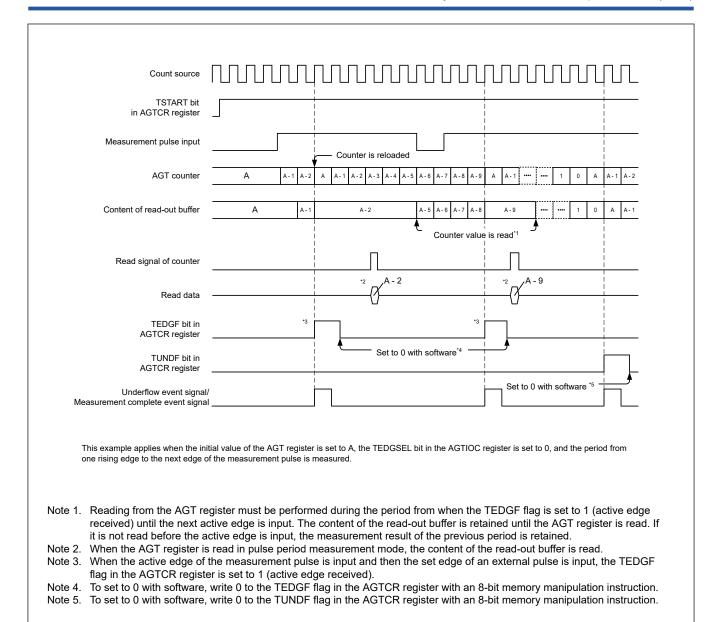

|    | 21.3.7       | Pulse Period Measurement Mode                                        | 436 |

|    | 21.3.8       | Compare Match function                                               | 437 |

|    | 21.3.9       | Output Settings for Each Mode                                        | 438 |

|    | 21.3.10      | Standby Mode                                                         | 439 |

|    | 21.3.11      | Interrupt Sources                                                    | 440 |

|    | 21.3.12      | Event Signal Output to ELC                                           |     |

|    | 21.4 Usage   | Notes                                                                | 440 |

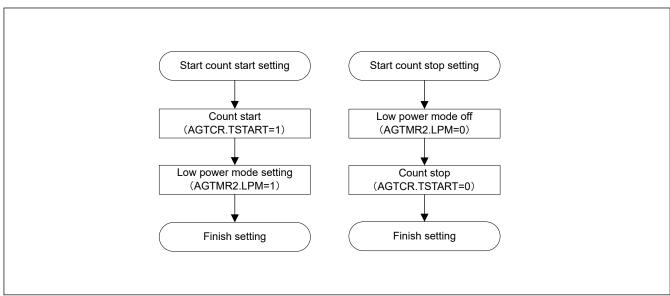

|    | 21.4.1       | Count Operation Start and Stop Control                               | 440 |

|    | 21.4.2       | Access to Counter Register                                           |     |

|    | 21.4.3       | When Changing Mode                                                   | 441 |

|    | 21.4.4       | Output pin setting                                                   | 441 |

|    | 21.4.5       | Digital Filter                                                       |     |

|    | 21.4.6       | How to Calculate Event Number, Pulse Width, and Pulse Period         | 442 |

|    | 21.4.7       | When Count is Forcibly Stopped by TSTOP Bit                          |     |

|    | 21.4.8       | When Selecting AGT0 Underflow as the Count Source                    | 442 |

|    |              |                                                                      |     |

|     | 2    | 1.4.9     | Module-stop function                                                                | 442  |

|-----|------|-----------|-------------------------------------------------------------------------------------|------|

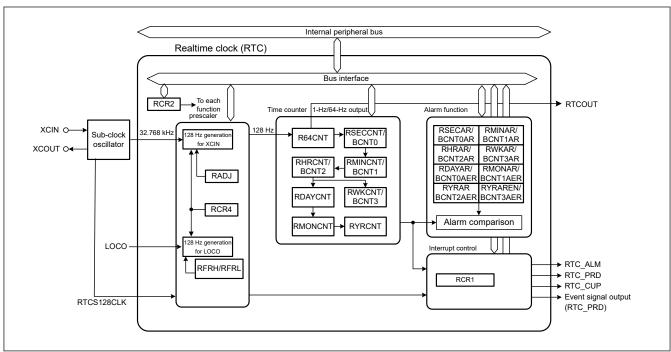

| 22. | Real | Itime Clo | ock (RTC)                                                                           | 443  |

|     | 22.1 | Overvie   | ew                                                                                  | .443 |

|     | 22.2 | Registe   | r Descriptions                                                                      | 444  |

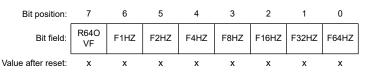

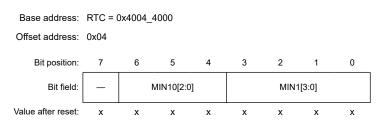

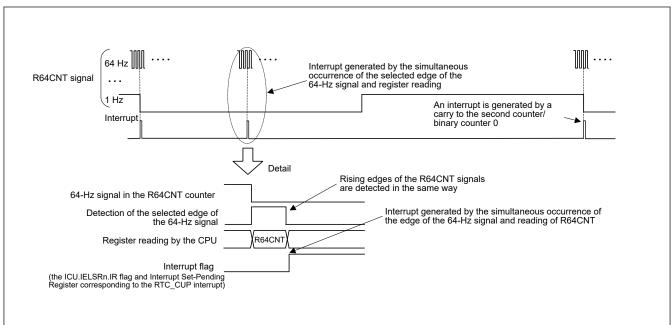

|     | 22   | 2.2.1     | R64CNT : 64-Hz Counter                                                              | 444  |

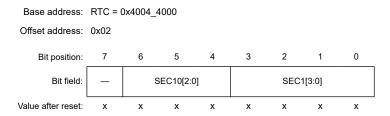

|     | 22   | 2.2.2     | RSECCNT : Second Counter (in Calendar Count Mode)                                   | 445  |

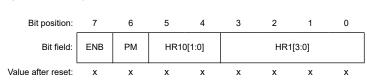

|     | 22   | 2.2.3     | RMINCNT : Minute Counter (in Calendar Count Mode)                                   | 445  |

|     | 22   | 2.2.4     | RHRCNT : Hour Counter (in Calendar Count Mode)                                      | 446  |

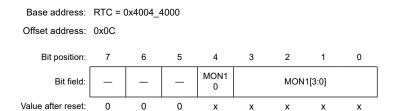

|     | 22   | 2.2.5     | RWKCNT : Day-of-Week Counter (in Calendar Count Mode)                               | 446  |

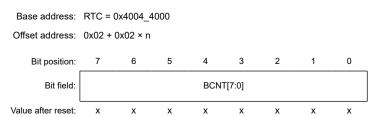

|     | 22   | 2.2.6     | BCNTn : Binary Counter n (n = 0 to 3) (in Binary Count Mode)                        | 447  |

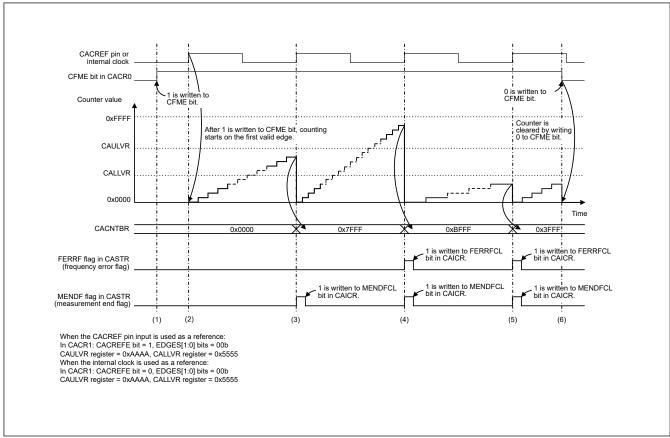

|     | 22   | 2.2.7     | RDAYCNT : Day Counter                                                               | 447  |